前言

本文聚焦问题——不同综合与实现策略是否影响编译速度及影响程度。以Vivado 2024.2为环境,选取CPU、MB、ZYNQU、VCT工程测试,对比默认与编译时间优化策略的耗时,剖析策略作用,为Vivado编译提速提供参考。

一、实验条件说明

-

使用CPU、MB、ZYNQU和VCT作为测试工程 -

Vivado版本为2024.2 -

测试编译时间优化策略相对默认策略能缩短多少编译时间

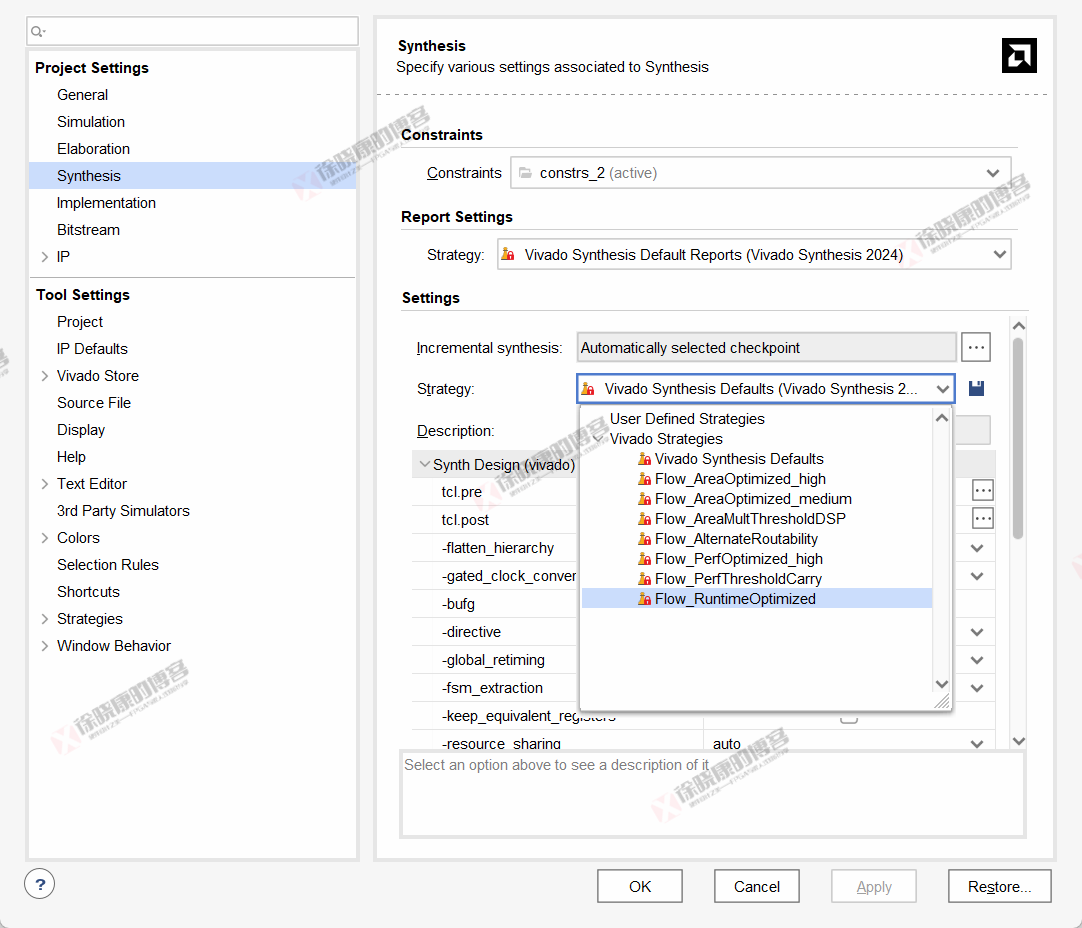

如何设置编译时间优化策略:打开Vivado工程 -> 设置 -> Synthesis/Implementation -> 选择策略为Flow_RuntimeOptimized,如下图所示。

二、测试截图

2.1 默认策略

因本系列的前几篇文章都是用的默认策略,所以这里的测试截图与前几篇文中是一样的,这里仅为提高本文的独立性而保留。

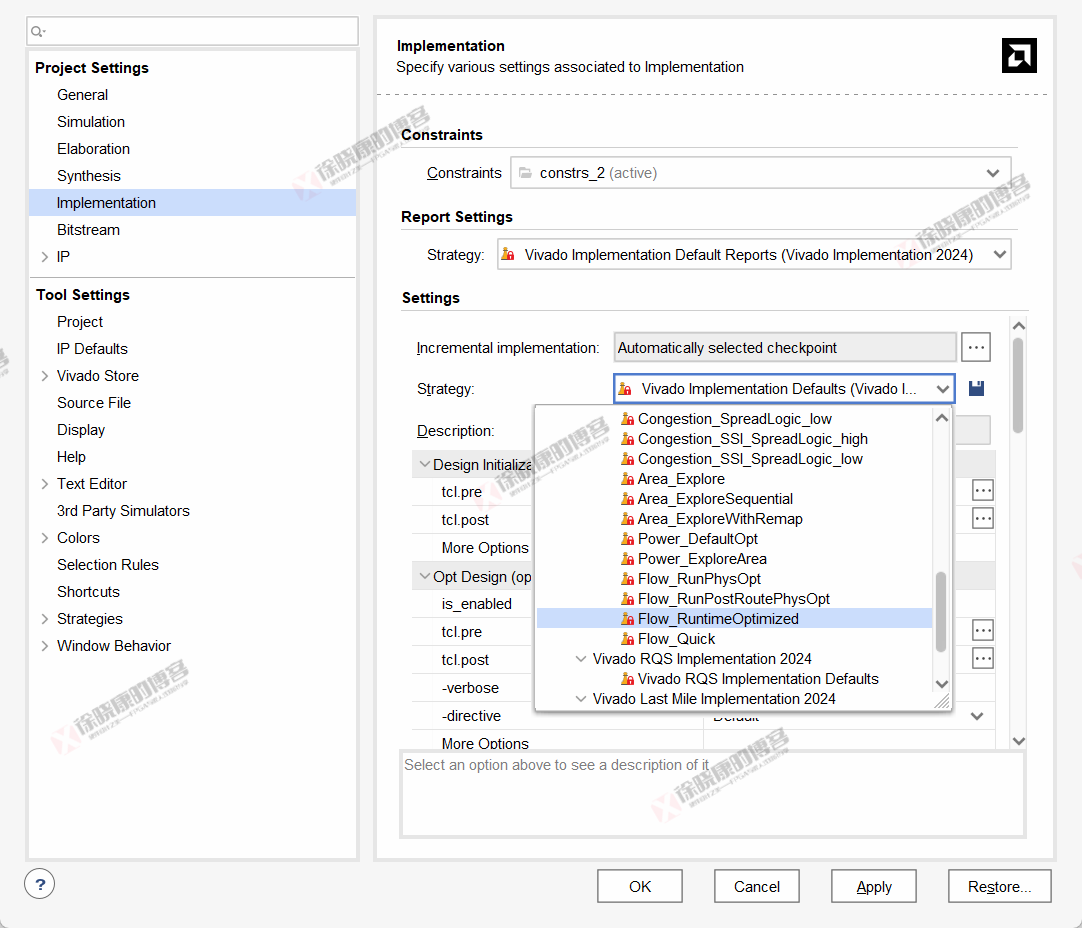

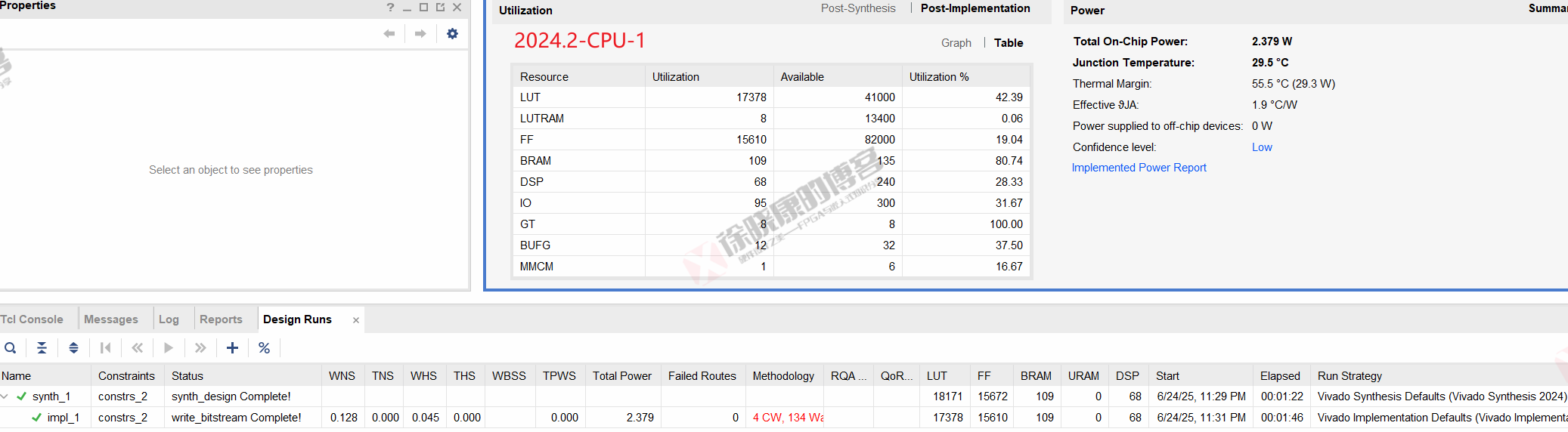

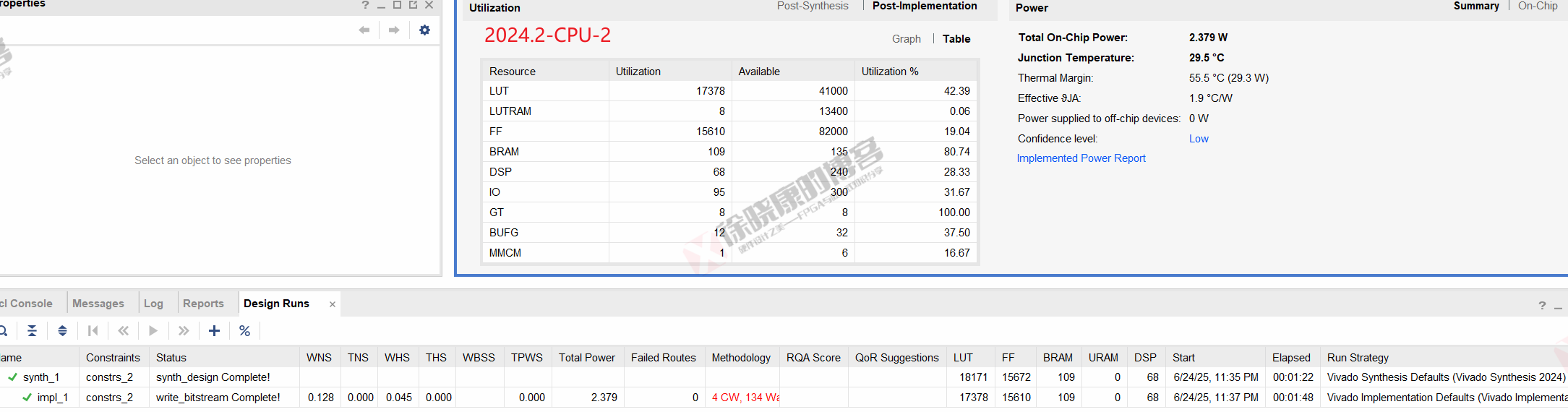

CPU

| 实验编号 | OOC | 综合 | 实现 | 合计 |

|---|---|---|---|---|

| 默认策略-CPU-1 | 0 | 1m22s | 1m46s | 3m08s |

| 默认策略-CPU-2 | 0 | 1m22s | 1m48s | 3m10s |

| 默认策略-CPU-平均 | 0 | 1m22s | 1m47s | 3m09s |

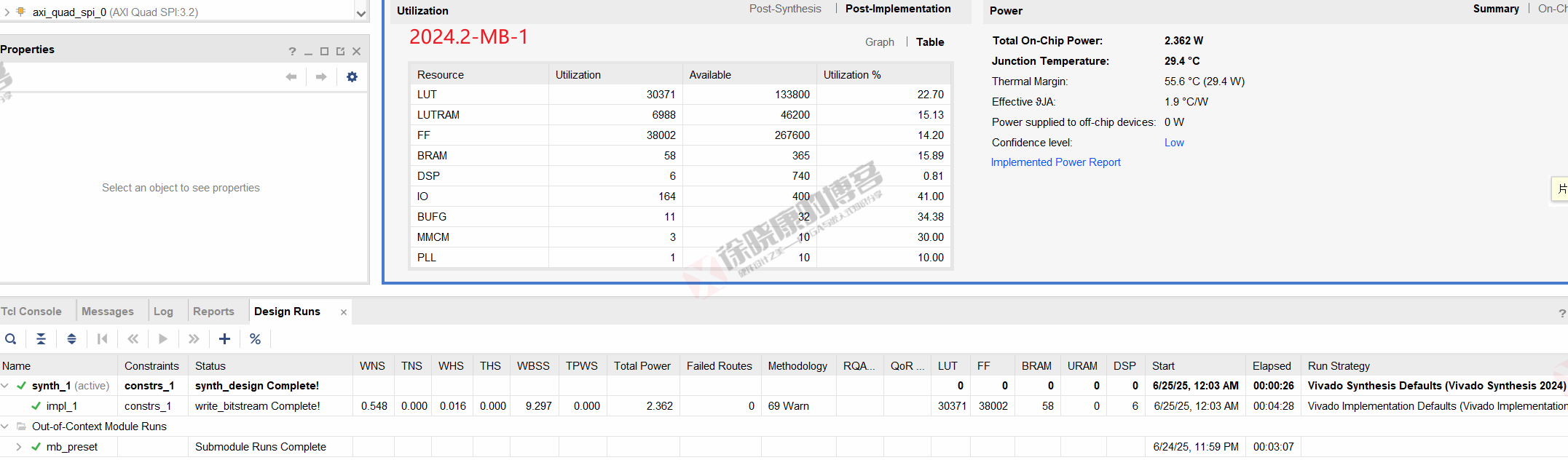

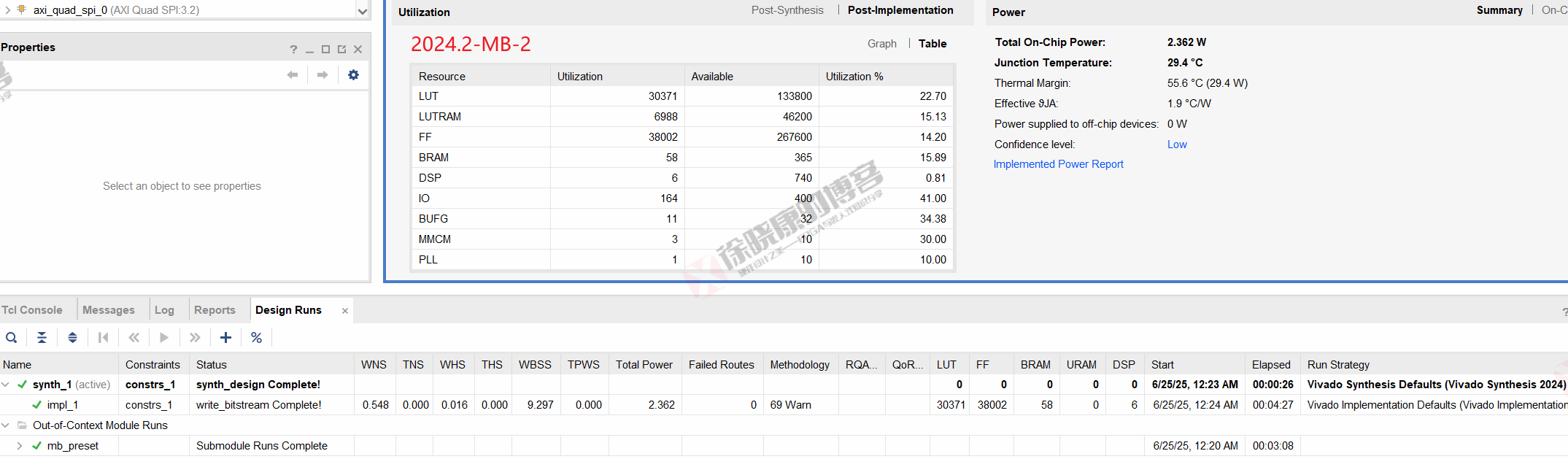

MB

| 实验编号 | OOC | 综合 | 实现 | 合计 |

|---|---|---|---|---|

| 默认策略-MB-1 | 3m07s | 26s | 4m28s | 8m01s |

| 默认策略-MB-2 | 3m08s | 26s | 4m27s | 8m01s |

| 默认策略-MB-平均 | 3m07.5s | 26s | 4m27.5s | 8m01s |

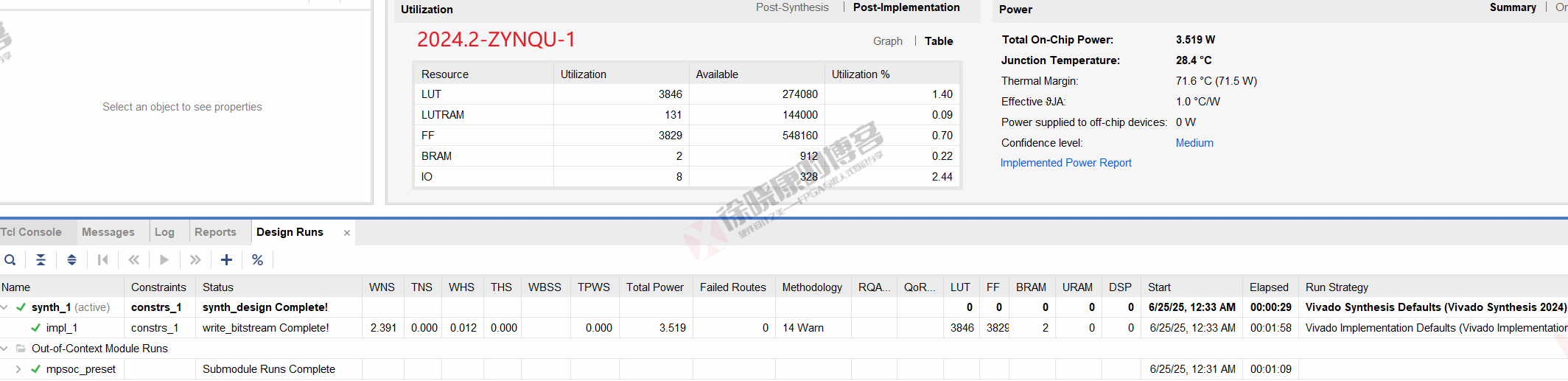

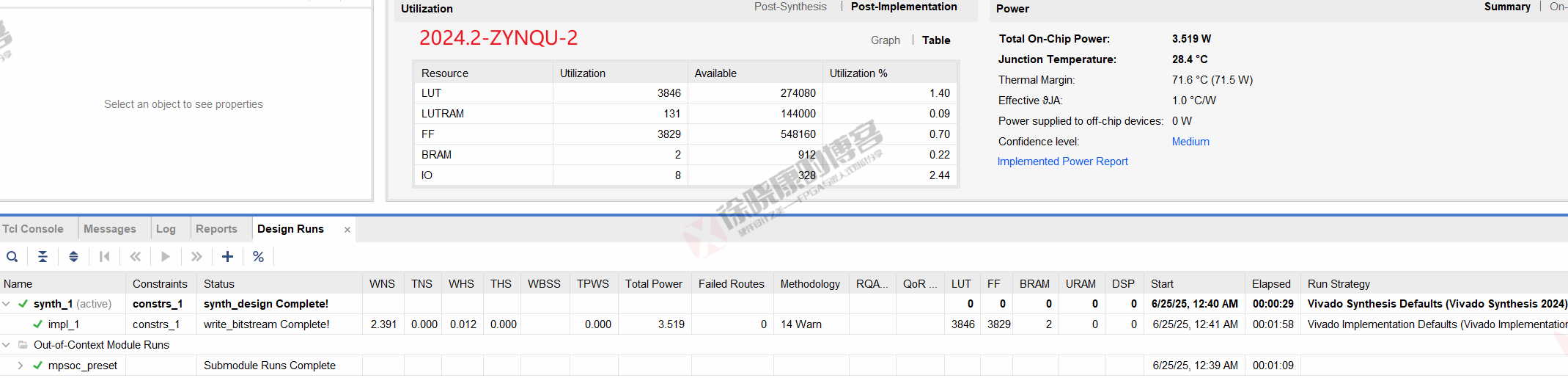

ZYNQU

| 实验编号 | OOC | 综合 | 实现 | 合计 |

|---|---|---|---|---|

| 默认策略-ZYNQU-1 | 1m09s | 29s | 1m58s | 3m36s |

| 默认策略-ZYNQU-2 | 1m09s | 29s | 1m58s | 3m36s |

| 默认策略-ZYNQU-平均 | 1m09s | 29s | 1m58s | 3m36s |

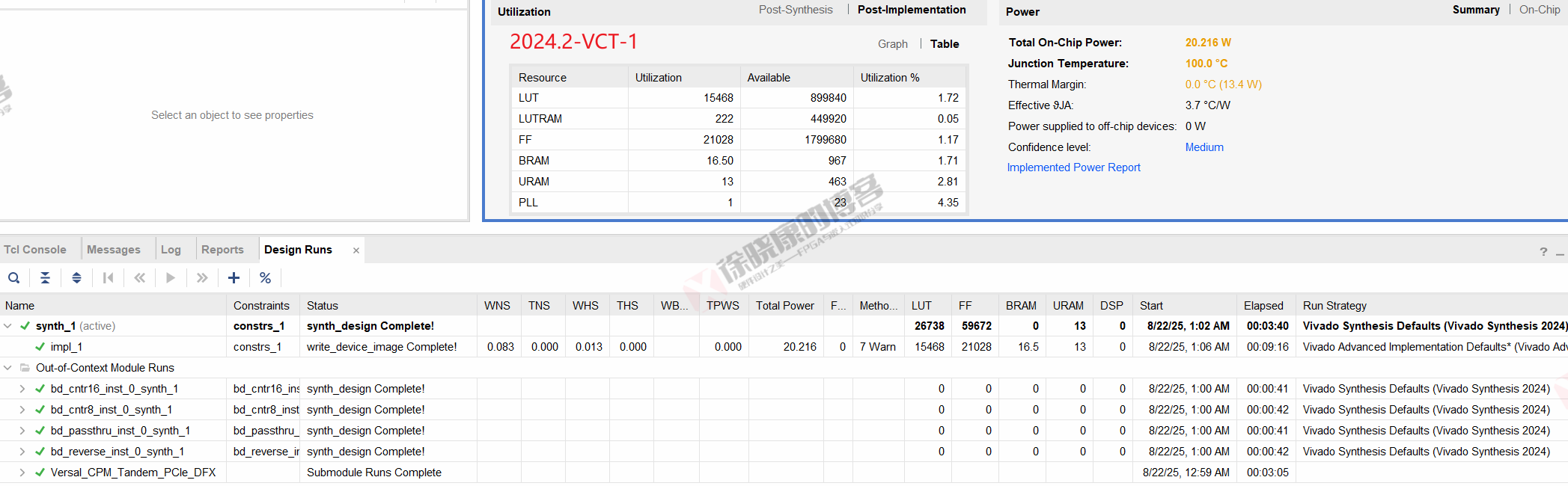

VCT

| 实验编号 | OOC | 综合 | 实现 | 合计 |

|---|---|---|---|---|

| 默认策略-VCT-1 | 3m05s | 3m40s | 9m16s | 16m01s |

| 默认策略-VCT-2 | 3m06s | 3m39s | 9m16s | 16m01s |

| 默认策略-VCT-平均 | 3m05.5s | 3m39.5s | 9m16s | 16m01s |

2.2 编译时间优化策略

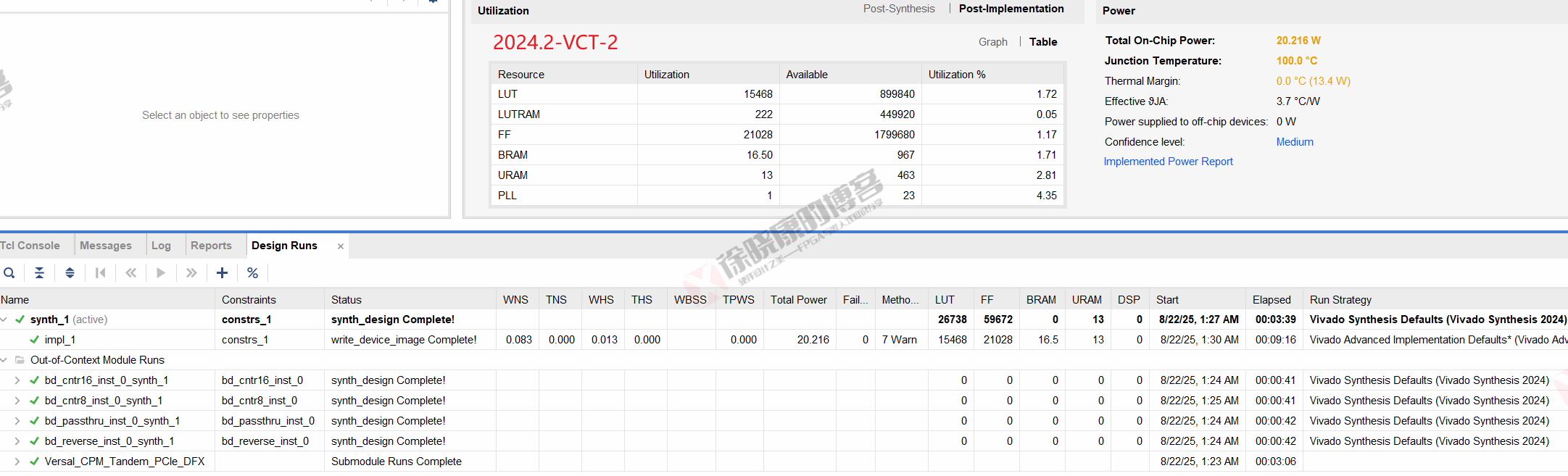

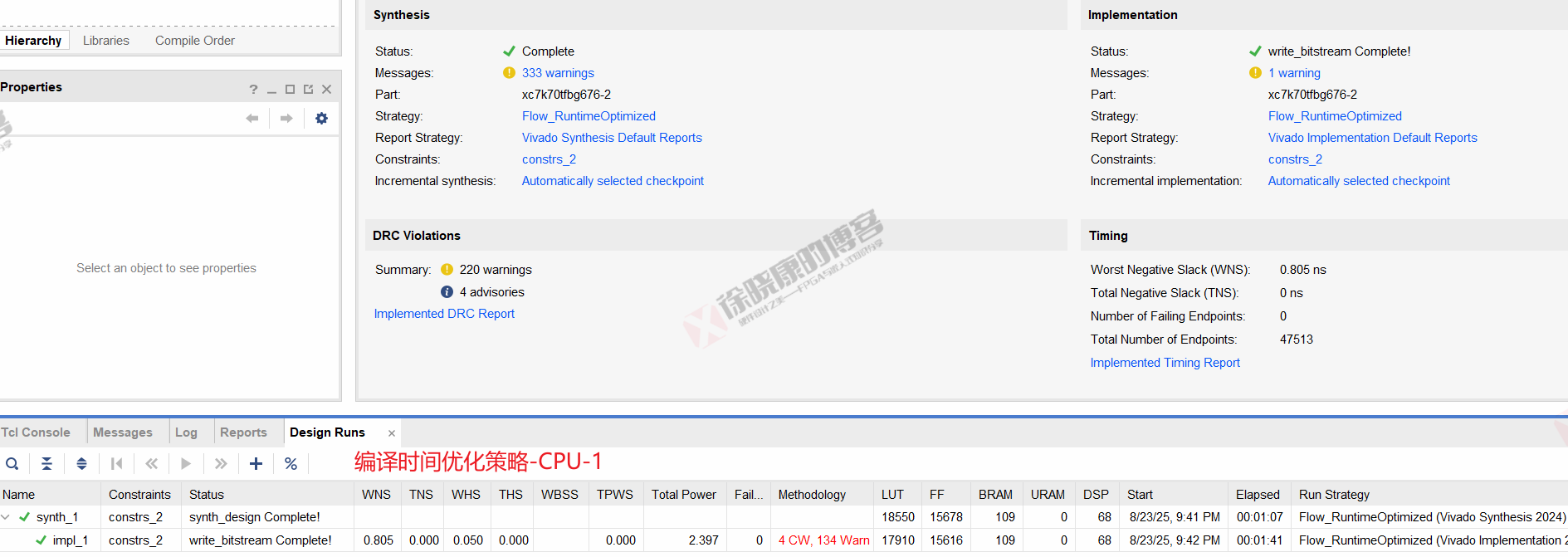

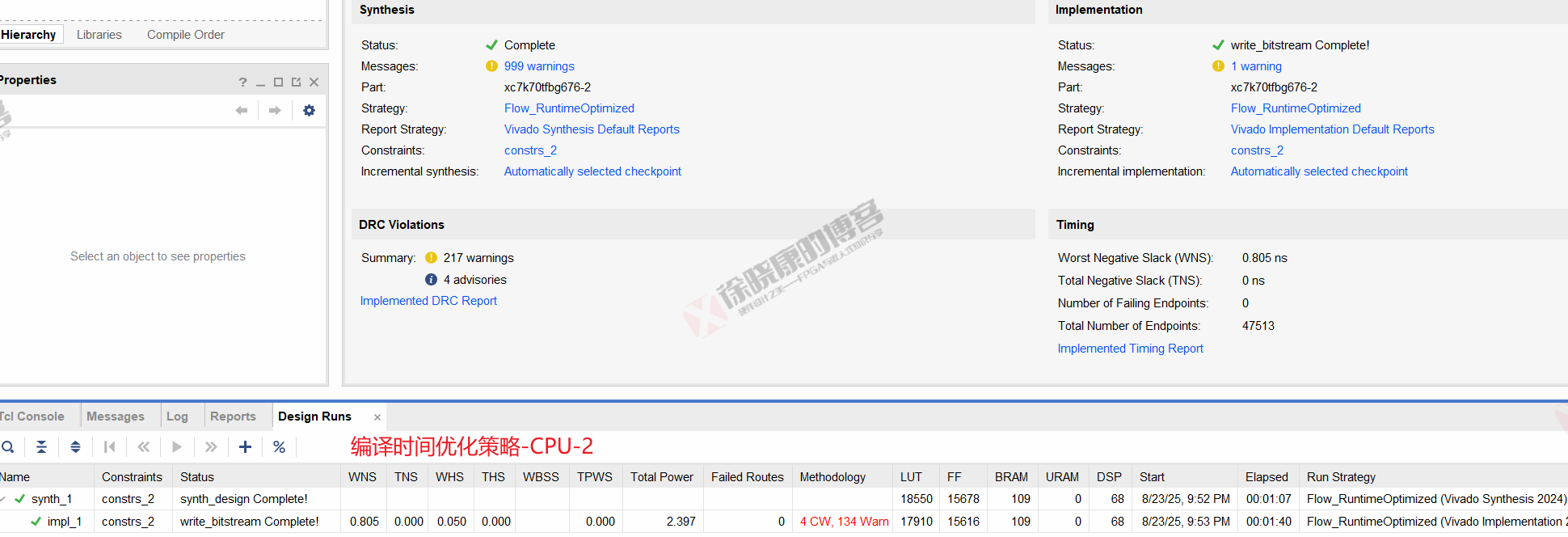

CPU

| 实验编号 | OOC | 综合 | 实现 | 合计 |

|---|---|---|---|---|

| 编译时间优化策略-CPU-1 | 0 | 1m07s | 1m40s | 2m47s |

| 编译时间优化策略-CPU-2 | 0 | 1m07s | 1m41s | 2m48s |

| 编译时间优化策略-CPU-平均 | 0 | 1m07s | 1m40.5s | 2m47.5s |

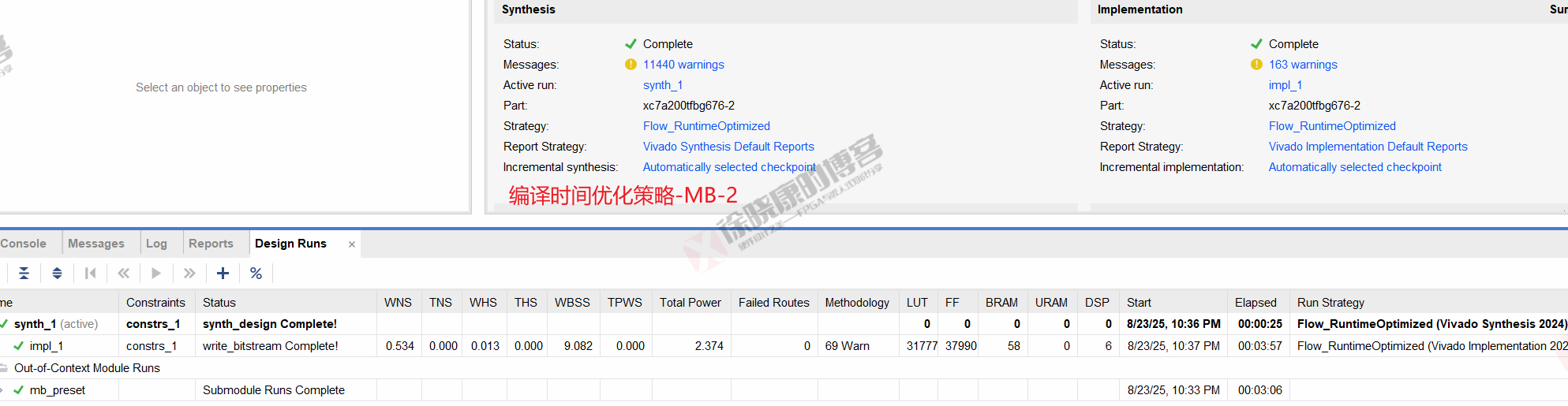

MB

| 实验编号 | OOC | 综合 | 实现 | 合计 |

|---|---|---|---|---|

| 编译时间优化策略-MB-1 | 3m02s | 25s | 3m56s | 7m23s |

| 编译时间优化策略-MB-2 | 3m06s | 25s | 3m57s | 7m28s |

| 编译时间优化策略-MB-平均 | 3m04s | 25s | 3m56.5s | 7m25.5s |

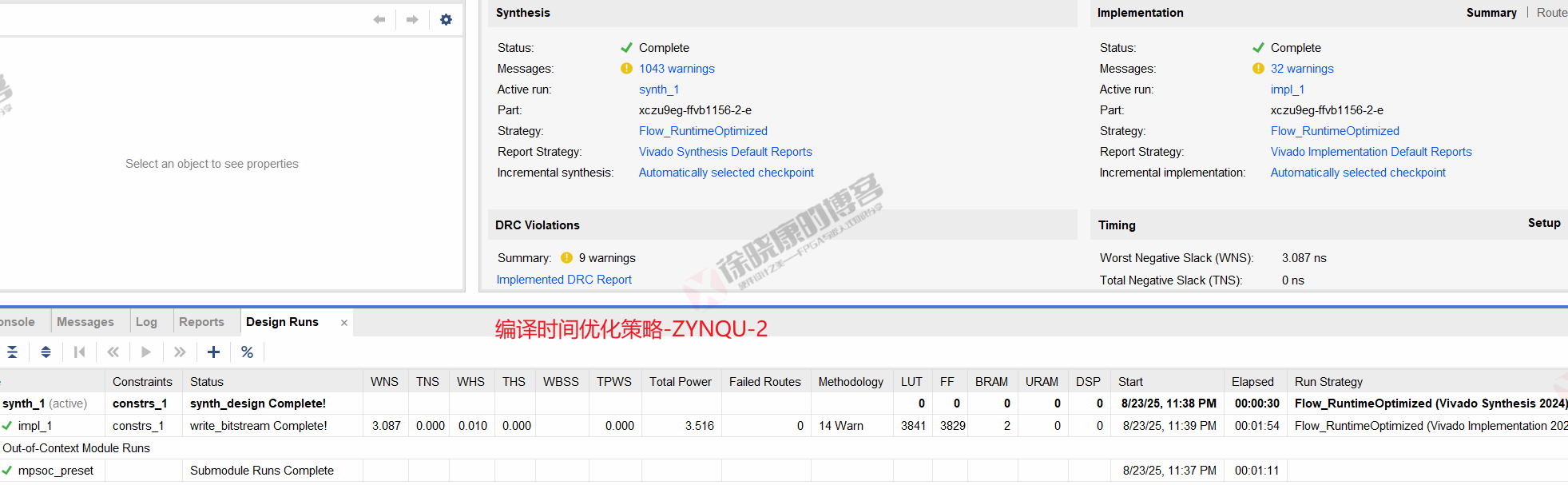

ZYNQU

| 实验编号 | OOC | 综合 | 实现 | 合计 |

|---|---|---|---|---|

| 编译时间优化策略-ZYNQU-1 | 1m08s | 29s | 1m53s | 3m30s |

| 编译时间优化策略-ZYNQU-2 | 1m11s | 30s | 1m54s | 3m35s |

| 编译时间优化策略-ZYNQU-平均 | 1m09.5s | 29.5s | 1m53.5s | 3m32.5s |

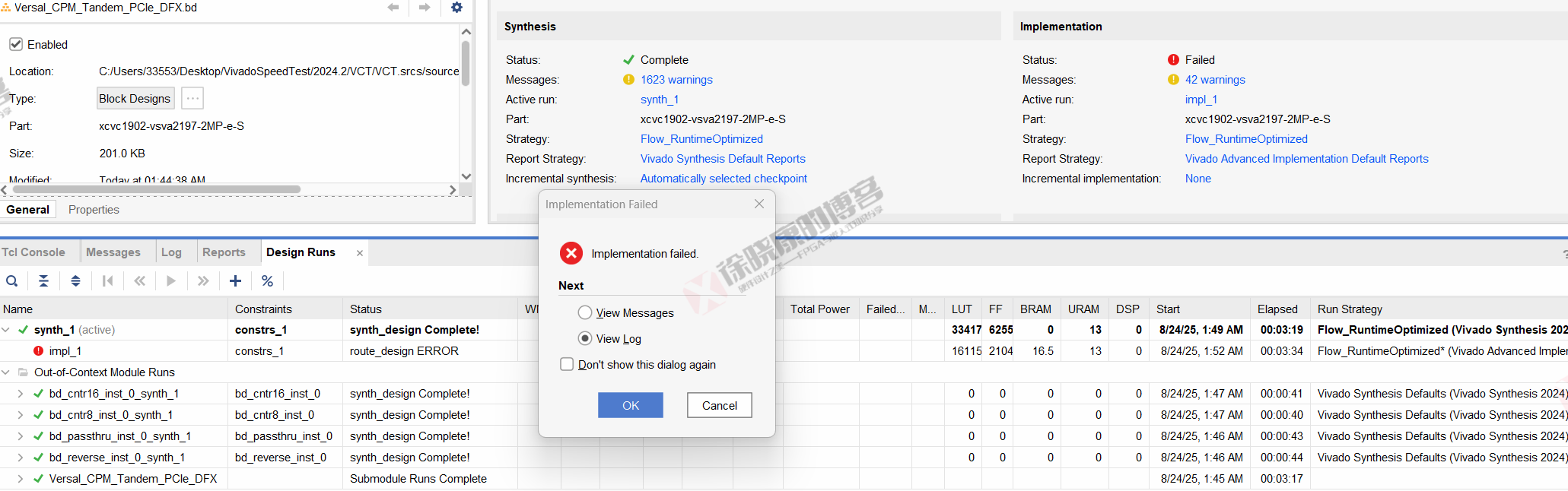

VCT

用编译时间优化策略跑了4~5次,都在实现阶段失败了,且必定失败在3m34s左右。

这个实现阶段失败的原因,有几种可能:

-

内存溢出,但我打开任务管理器一直监控内存状态,发现Vivado从头到尾内存都未超过50%,所以,正常情况下,电脑的64GB内存是完全够用的。但是,实现阶段,尤其是布局布线(Place & Route),会有瞬时峰值内存需求,这个峰值可能非常高且短暂,任务管理器可能很难捕捉到,但它足以触发操作系统终止进程,所以,也不排除有这种瞬间峰值内存的可能性; -

Vivado 2024.2自身问题,在编译时间优化策略下就是无法实现成功,换Vivado 2025.1同样的工程,同样的策略测试一下。

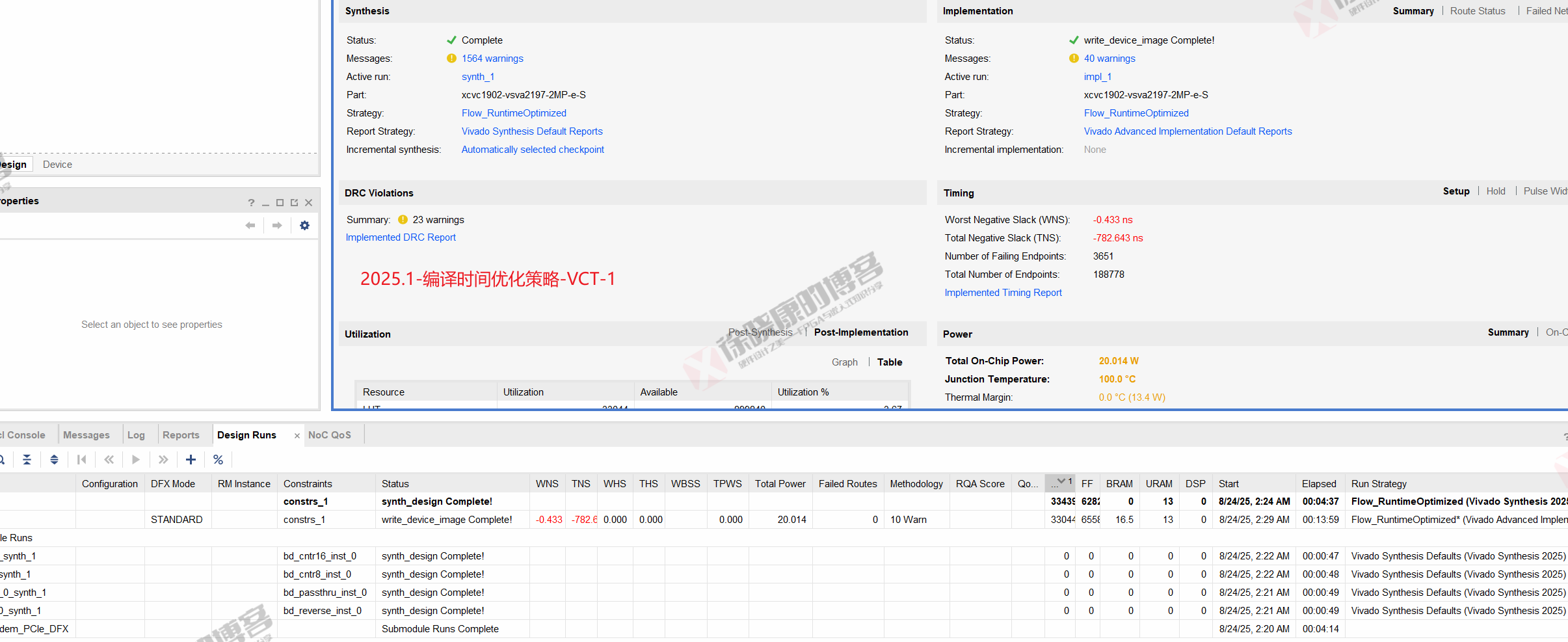

2025.1-编译时间优化策略-VCT

可见,确实可能是Vivado 2024.2软件自身的问题,在编译速度更快的同时,稳定性可能相对2025.1稍差。

| 实验编号 | OOC | 综合 | 实现 | 合计 |

|---|---|---|---|---|

| 2024.2-默认策略-VCT-1 | 3m05.5s | 3m39.5s | 9m16s | 16m01s |

| 2024.2-编译时间优化策略-VCT-1 | 3m17s | 3m19s | — | — |

| 2025.1-编译时间优化策略-VCT-1 | 4m14s | 4m37s | 13m59s | 22m50s |

从上述表格可以发现,2025.1即使在编译时间优化策略下,也比2024.2慢了42.6%,这也太慢了,所以,我认为还是应该使用Vivado 2024.2,毕竟实现出错只是小概率事件。

三、实验结果统计与分析

| 实验条件/平均编译时间/示例工程 | CPU | MB | ZYNQU | VCT |

|---|---|---|---|---|

| 默认策略 | 3m09s | 8m01s | 3m36s | 16m01s |

| 编译时间优化策略 | 2m47.5s (-11.4%) |

7m25.5s (-7.4%) |

3m32.5s (-1.6%) |

— |

由以上实验数据我们可以得出结论:

-

编译时间优化策略有时能提高一些编译速度,但效果并不明显,进一步对比会发现,时间主要缩短在实现阶段; -

编译时间优化策略并不总是起作用,在ZYNQU工程中它就没有作用; -

编译时间优化策略可能导致实现失败(如在VCT工程中),一个可能的原因是编译时间优化策略的时序优化能力较差,使得复杂工程中时序难以满足要求,进而导致Vivado反复尝试去满足时序要求,最终导致实现失败。

建议:如果电脑确实跑得比较慢,本着能节约点时间也好的想法,可以在开发前期尝试下编译时间优化策略,对比下与默认策略相比编译时间能缩短多少,开发后期再换回默认策略或其他优化面积/速度的策略,这样能加快些开发进度。

如果发现编译出错,及时换回默认策略。

Vivado的综合和实现的策略选择很多,因本系列文章仅关注编译速度,故未尝试其他策略,感兴趣的同学可自行尝试。

四、测试工程分享

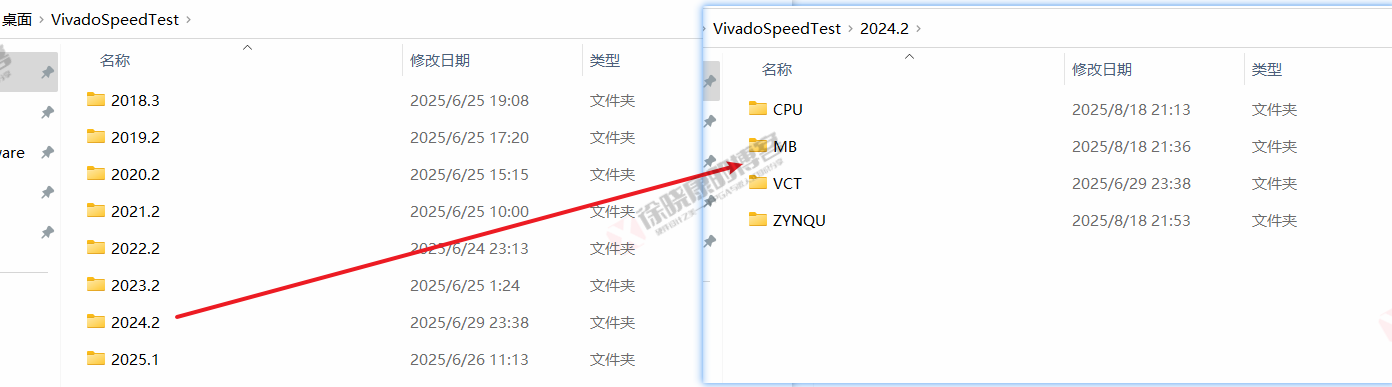

本系列文章的所有测试工程,如下图所示。

均通过网盘分享。

欢迎大家关注我的微信公众号:徐晓康的博客,回复以下6位数字获取网盘链接。

981520

建议复制过去不会码错字!

如果本文对你有所帮助,欢迎点赞、转发、收藏、评论让更多人看到,赞赏支持就更好了。

如果对文章内容有疑问,请务必清楚描述问题,留言评论或私信告知我,我看到会回复。

徐晓康的博客持续分享高质量硬件、FPGA与嵌入式知识,软件,工具等内容,欢迎大家关注。