前言

在FPGA开发中,Vivado编译的漫长过程一直是限制开发效率的主要瓶颈之一。那么,怎么提高Vivado的编译速度呢?一般的思路是以下几个:

-

Vivado多线程设置,Vivado默认最大线程为2,设置到最大的32线程,是否可以让Vivado编译更快? -

同一CPU,运行频率越高(超频),Vivado是不是编译更快? -

内存大小足够时,内存读写频率越高,Vivado是不是编译越快? -

选择特定的Vivado版本,如Vivado 2024.2是不是比Vivado 2021.2编译更快? -

Ubuntu系统下的Vivado是不是比Windows下的编译更快? -

禁用非必要报告/信息是否速度更快? -

不同的综合/实现策略是否影响编译速度?影响有多大? -

不使用GUI界面,只用CMD运行TCL命令编译Vivado工程,是否速度更快? -

Vivado有两种开发方式,Project Mode和Non-Project Mode,哪种速度更快? -

使用模块化综合(Out-of-Context, OOC)是否速度更快? -

增量编译可加快除第一次外的编译速度,怎么设置?

本系列文章将设置不同条件对Vivado编译速度进行详细测试,评估哪些手段能提高Vivado的编译速度。

注:这里的“编译”是借用的一些高级语言(如C语言)的说法,表示从代码生成比特流这一过程。对于硬件描述语言(HDL),这一流程的标准说法是综合(Synthesis)+实现(Implementation)。但“编译”一词已深入人心,且更简洁,所以本文还是使用“编译”一词。

一、电脑与操作系统信息

本系列文章所有测试均基于以下硬件平台。

| 硬件/软件 | 型号/版本 | 说明 |

|---|---|---|

| CPU | AMD 9950X | 16核32线程,基准主频4.3GHz,超频后最高频率约5.6GHz(除超频实验部分特意关闭了超频设置外,其它所有实验均在超频条件下进行) |

| 内存 | DDR5 32G×2 C32 | 基准读写速度5600MHz,内存超频后速度为6400MHz(同样,除超频实验特意关闭了内存超频设置外,其它所有实验均在内存超频条件下完成) |

| 硬盘 | 2T SSD | Vivado编译速度应与硬盘无关 |

| GPU | NVIDIA 2060S | Vivado编译速度应与GPU无关 |

| 操作系统 | Win11 专业版 24H2 | 因目前新推出的电脑不再支持Win10(当然Win10下也能用,但很多硬件驱动会有问题),故本系列实验对于Windows系统仅测试了Win11 |

二、测试实验设计思路

实验设计主要基于以下几点思路:

-

使用Vivado自带的示例工程,方便其他人复刻实验; -

选用中规模,中大规模,大规模三种规格同时也是三种不同芯片的示例工程,以排除特定芯片的影响; -

综合和实现策略均使用Vivado各版本自带的 默认策略; -

编译期间,关闭杀毒软件、浏览器、办公软件等可能占用CPU和内存的应用程序,关掉任务管理器中除Vivado外的所有程序,仅允许部分软件内存占用很少的软件在后台运行;确保Vivado能调用全部CPU和内存资源; -

保证Vivado软件总是处于前台(我发现这个在Win11系统真的很影响编译速度,挺奇怪的); -

单一变量,每项对比均保证单一变量。例如,要比较最大线程是否对Vivado编译速度有影响,那么就保证在其它变量(如电脑状态,后台运行软件,Vivado版本、测试工程等)完全一致的条件下进行实验; -

为防止偶然因素影响,每次编译实验进行两次(每次编译完成后,使用 reset_project命令即可复位工程到初始状态),两次编译的各项时间相差在10s以内认为实验有效,否则实验可能存在问题,最后取两次编译时间的平均值。(后续文章都展示了两次实验截图,但实际上每个实验条件都至少跑了4~10次,并确保每次编译时间都差不多)

三、测试用的示例工程

经过多次测试,最终选取以下三个Vivado自带示例工程作为测试工程。

这几个工程基本2018年之后的Vivado版本都包含,具有一般性。工程复杂度中等,编译时间不会太长,便于完成多轮测试。

注意:在Select Project Template(选择工程模版)界面,先点击Refresh将示例工程更新到最新版之后,再进行选择。

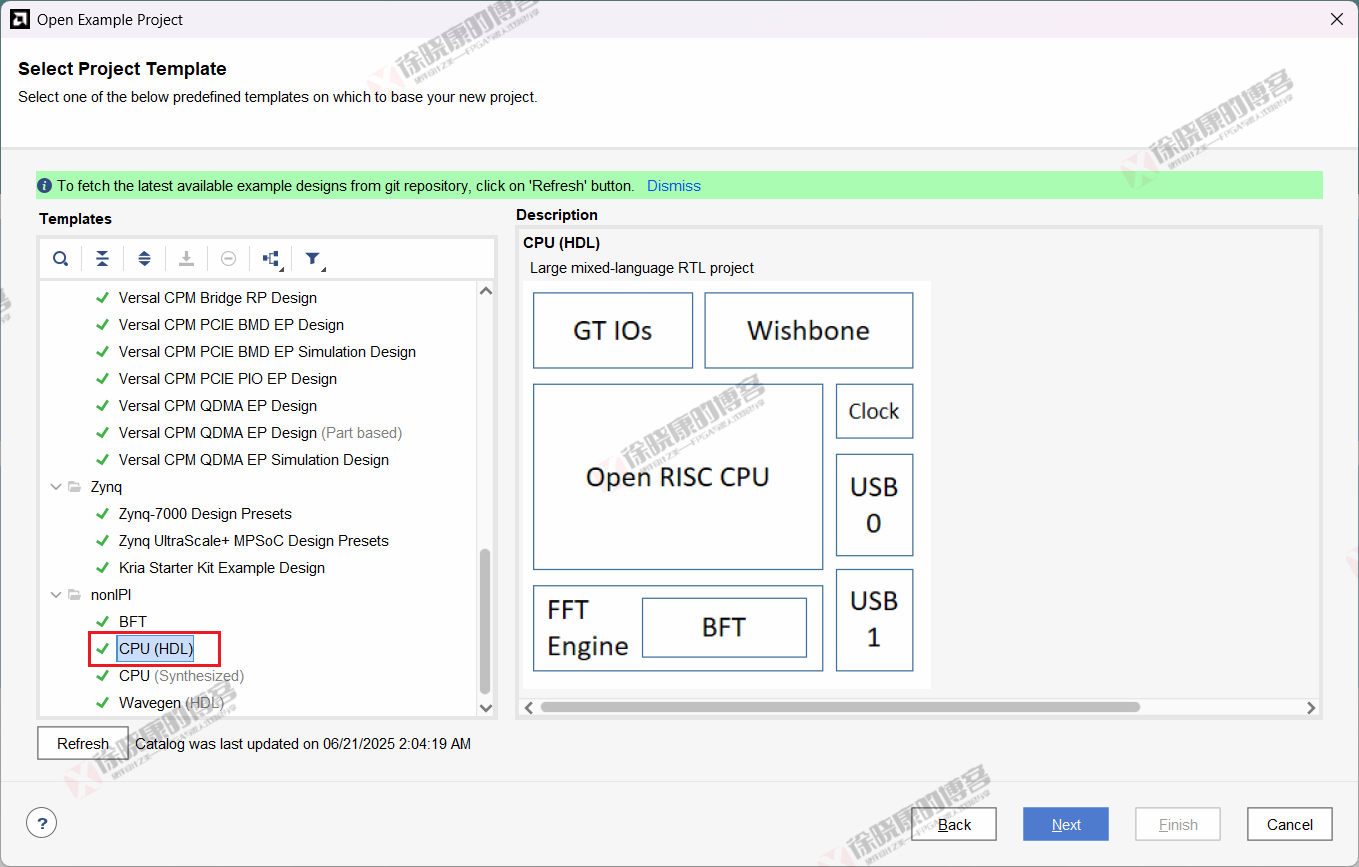

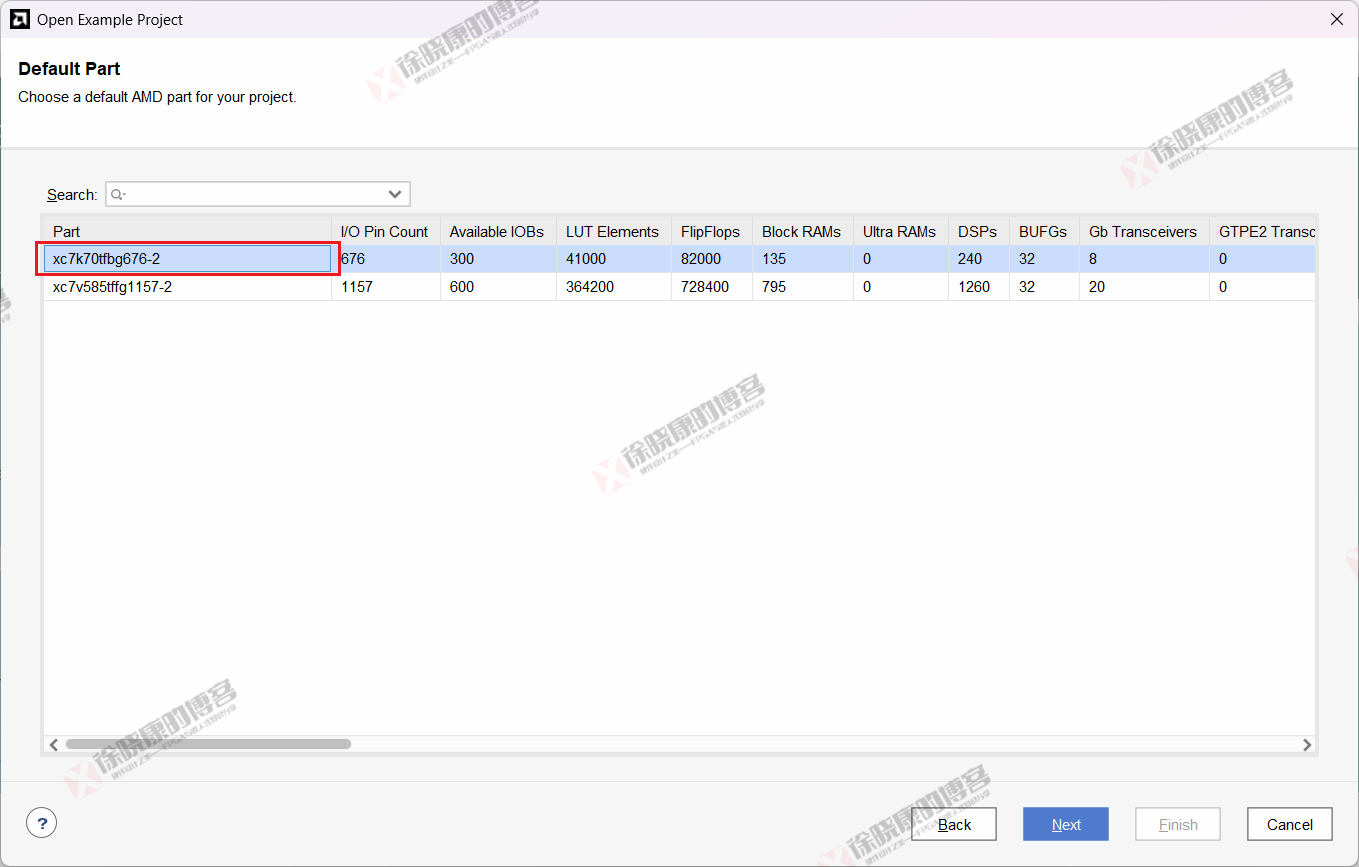

3.1 CPU(HDL)–xc7k70tfbg676-2

示例工程:CPU(HDL),芯片选择xc7k70tfbg676-2。

为便于说明,此实验条件后续简称为CPU。

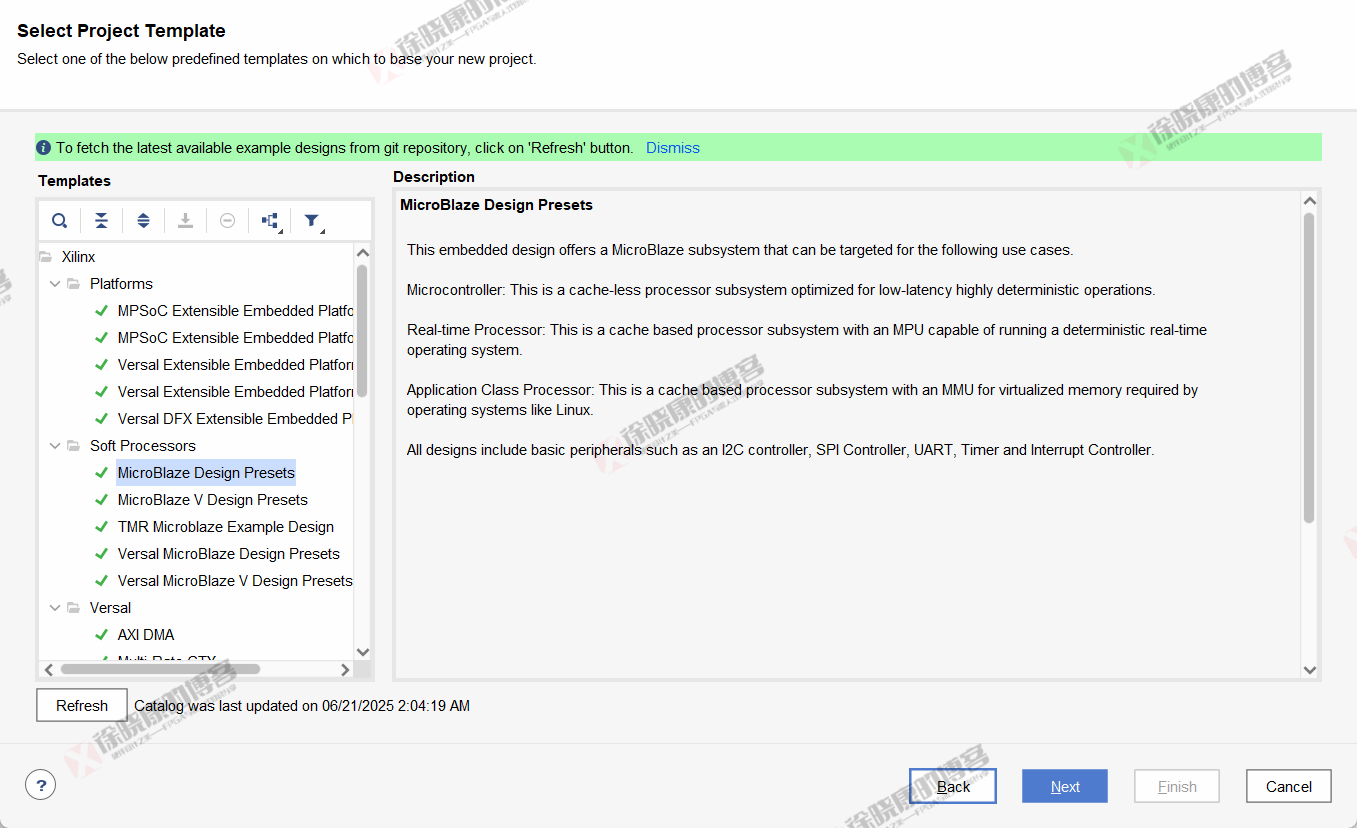

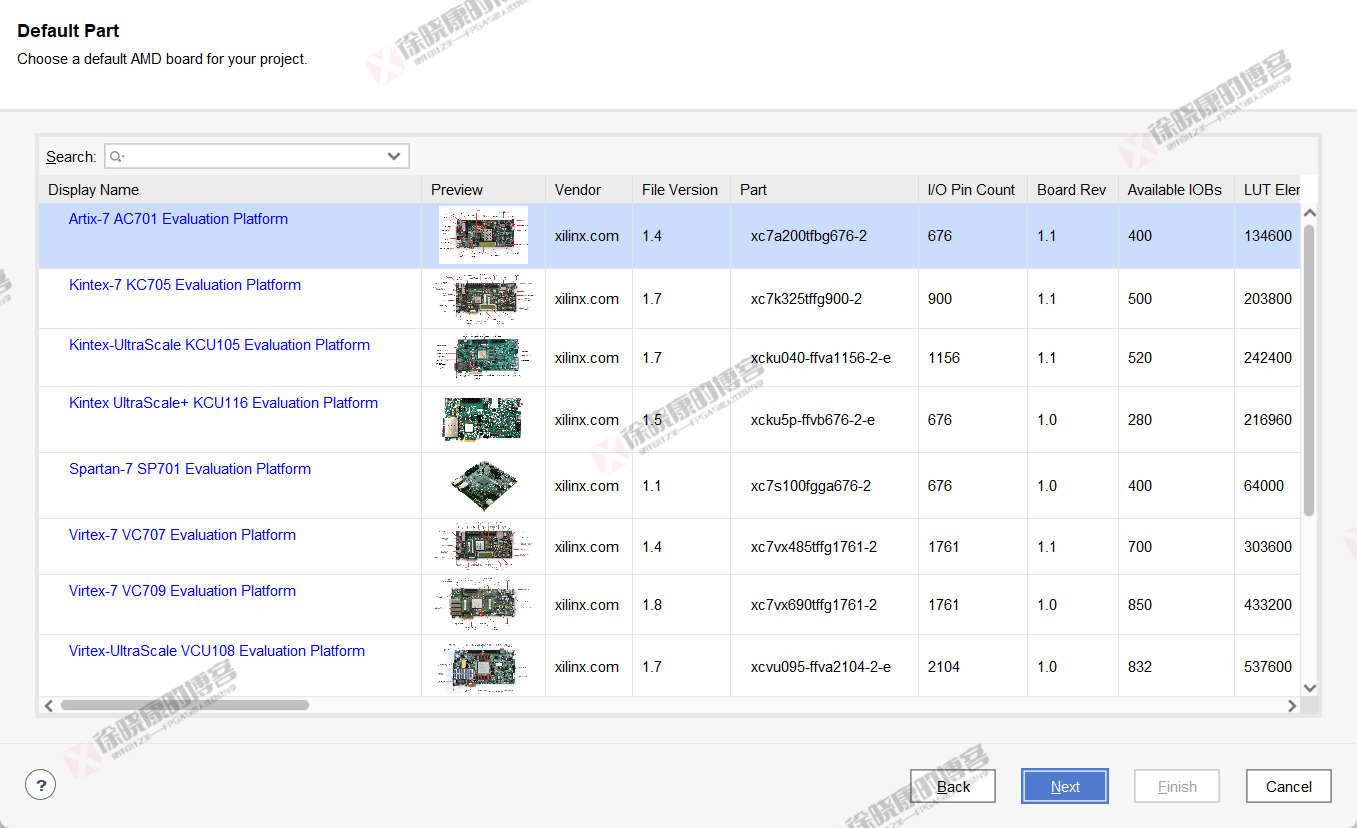

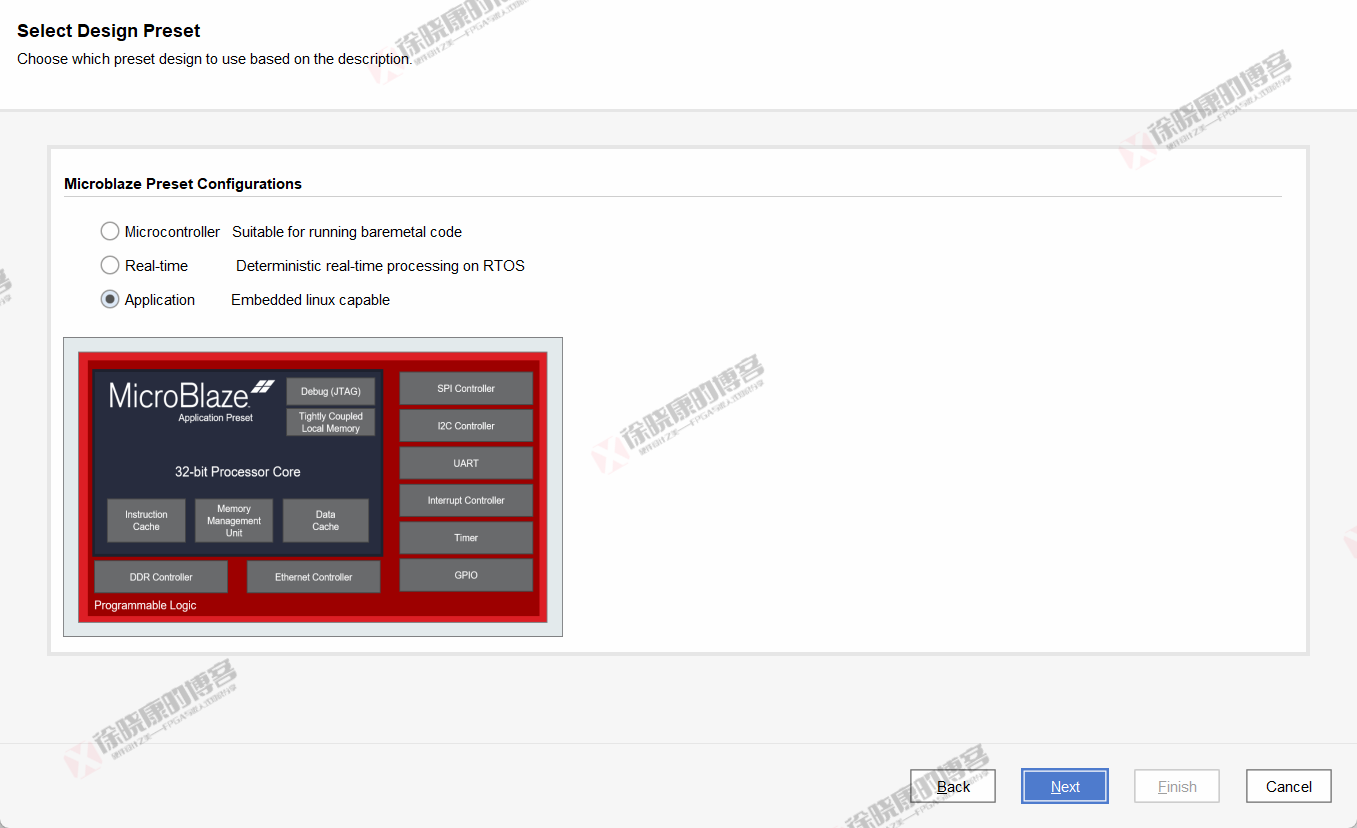

3.2 MicroBlaze Design Presets–Artix-7 AC701 Evaluation Platform

示例工程:MicroBlaze Design Presets,板卡选择Artix-7 AC701 Evaluation Platform(对应芯片为xc7a200tfbg676-2)。

为便于说明,此实验条件后续简称为MB。

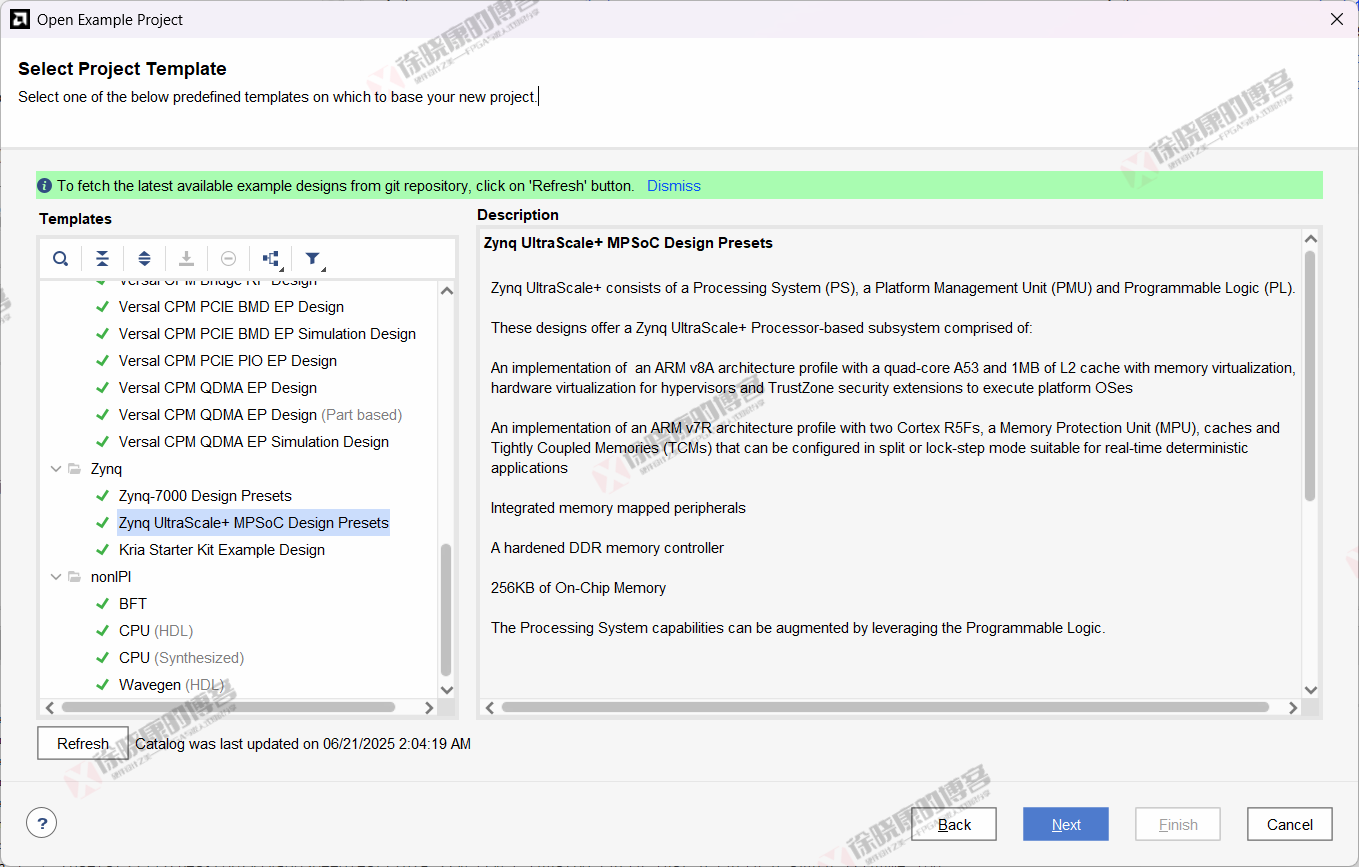

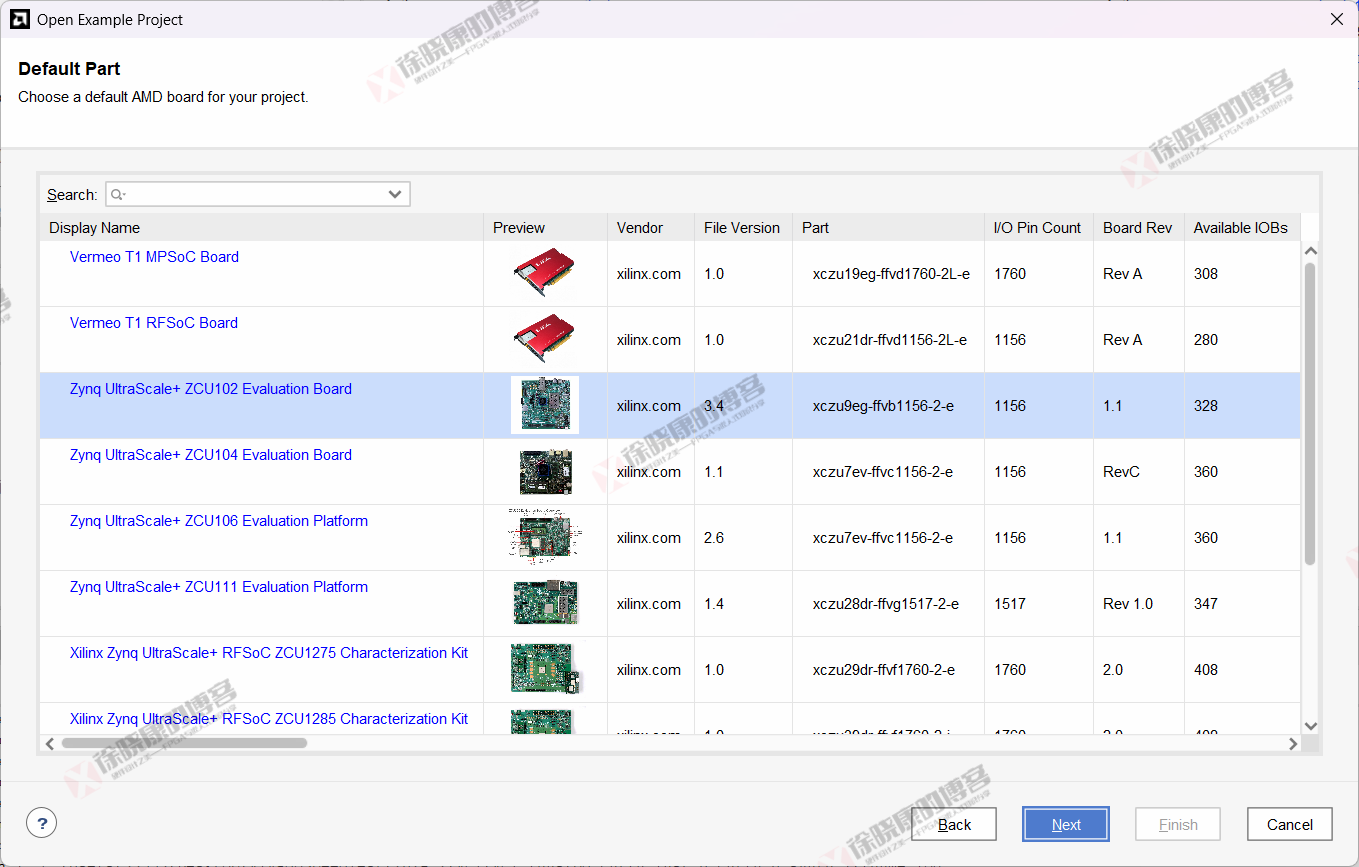

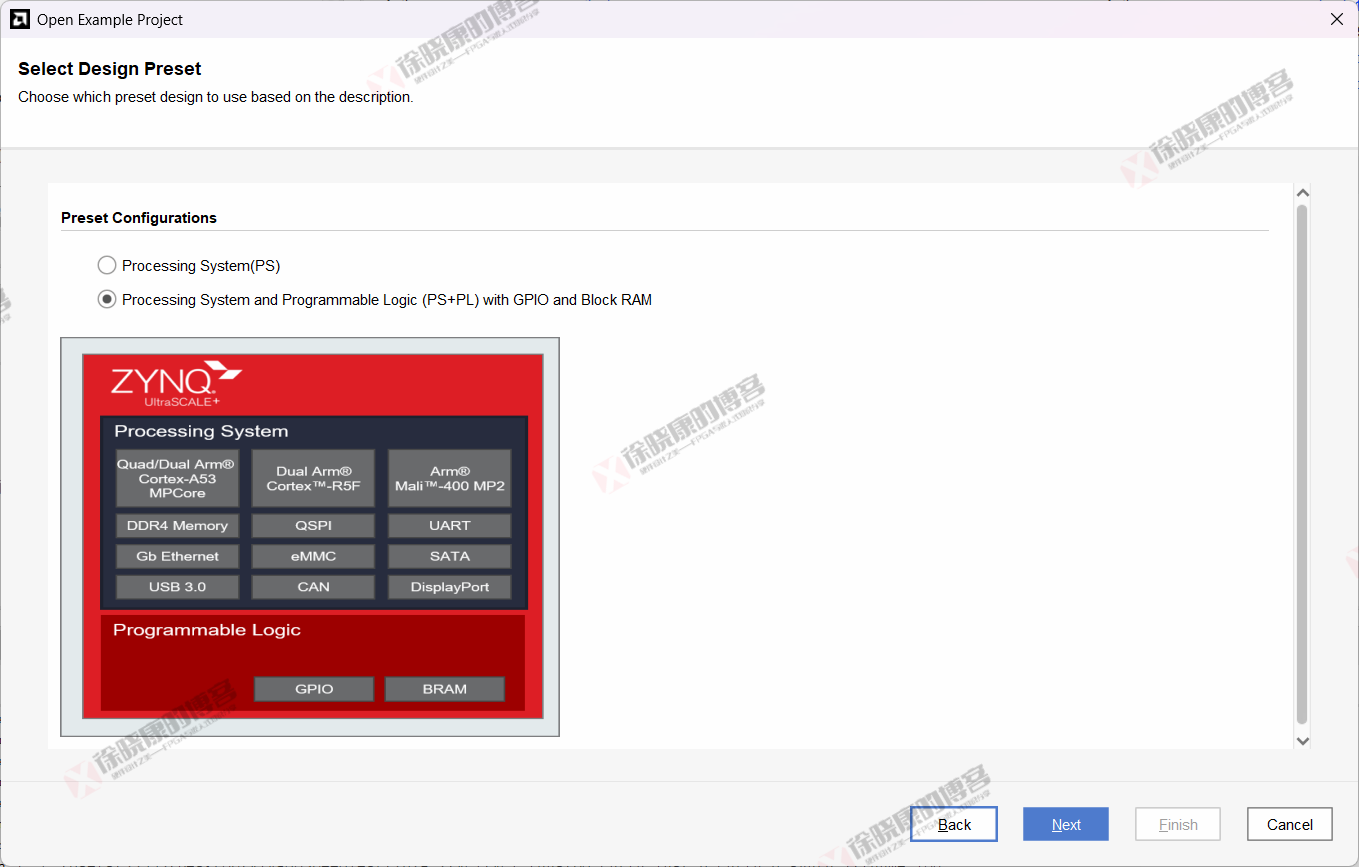

3.3 Zynq UltraScale+MPSoC Design Presets–Zynq UltraScale+ZCU102 Evaluation Board

示例工程:Zynq UltraScale+MPSoC Design Presets,板卡选择Zynq UltraScale+ZCU102 Evaluation Board(对应芯片为xczu9eg-ffvb1156-2-e)。

为便于说明,此实验条件后续简称为ZYNQU。

四、后续文章说明

后续文章将基于上述的硬件平台和测试工程,对Vivado编译速度进行多轮测试,主要关注的可能影响编译速度的点有:

-

线程数 -

CPU主频 -

内存读写速度 -

Vivado版本,如2018.3、2019.2、…、2024.2、2025.1等 -

操作系统,如Ubuntu -

…

敬请期待!

如果本文对你有所帮助,欢迎点赞、转发、收藏、评论让更多人看到,赞赏支持就更好了。

如果对文章内容有疑问,请务必清楚描述问题,留言评论或私信告知我,我看到会回复。

徐晓康的博客持续分享高质量硬件、FPGA与嵌入式知识,软件,工具等内容,欢迎大家关注。