相关文章:

Xilinx IP 解析之 Block Memory Generator v8.4 ——01-手册重点解读(仅Native RAM) – 徐晓康的博客

Xilinx IP 解析之 Block Memory Generator v8.4 ——02-如何配置 IP(仅 Native RAM) – 徐晓康的博客

Verilog功能模块–RAM和ROM(01)–功能说明与关键代码解析 – 徐晓康的博客

Verilog功能模块–RAM和ROM(02)–同步写-写冲突与读-写冲突实测 – 徐晓康的博客

Verilog 功能模块–RAM 和 ROM(03)–自编 RAM 与 Vivado RAM IP 功能对比实测 – 徐晓康的博客

前言

本系列文章介绍 Xilinx IP 核 Block Memory Generator v8.4,其实就是 Block RAM 和 Block ROM 的 IP 核。

此 IP 有两种接口的 BRAM:原生接口与 AXI 接口,本文仅介绍原生接口的BRAM。

本文介绍如何进行 IP 配置,对应 PG058 手册的第四章-Design Flow Steps的内容。

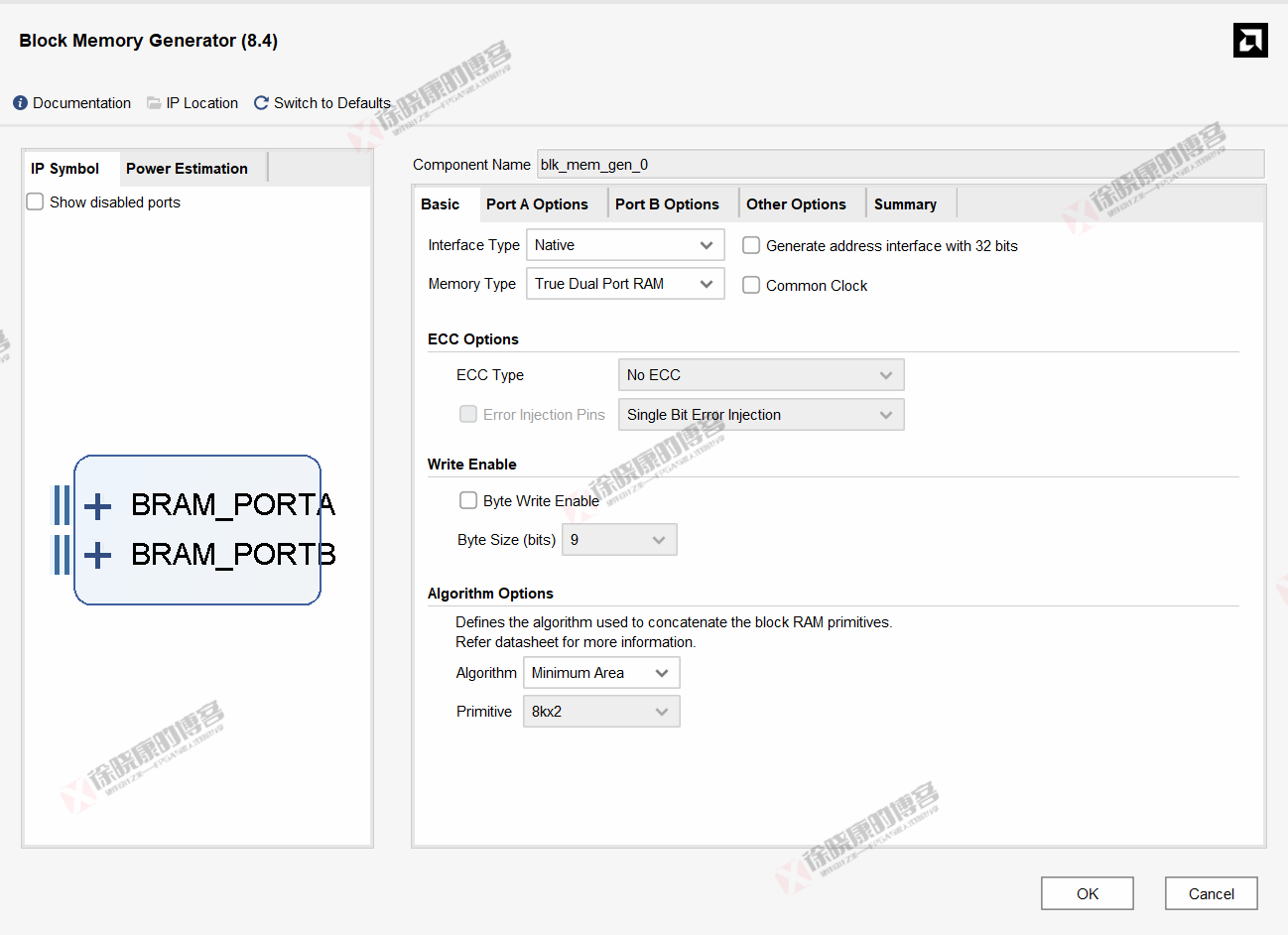

一、Basic(基本)

1.1 Basic

Interface Type:接口类型,可选 AXI4 或 Native,本文仅介绍 Native 接口即原生接口。

Generate address interface with 32 bits:生成 32 位地址。32 位地址的用处是可以与其他控制器采用统一的接口,可以统一寻址。

Memory Type:存储类型

-

Single Port RAM:单端口 RAM

-

Simple Dual Port RAM:简单双端口 RAM

-

True Dual Port RAM:真双端口 RAM

-

Single Port ROM:单端口 ROM

-

Dual Port ROM:双端口 ROM

Common Clock:同一时钟,定义双端口 RAM 的时钟是否是同一时钟,即 clka 和 clkb 是否连在一起。

1.2 ECC 选项(ECC Options)

ECC type:Error Correction Code type,纠错码类型。仅存储类型选择Simple Dual Port RAM时才能开启ECC功能。

-

Soft ECC:软纠错码,适用以下限制条件:-

支持数据宽度小于或等于 64 位的软纠错码。 -

使用汉明纠错码:可纠正单比特错误并检测双比特错误。 -

支持简单双端口随机存取存储器(Simple Dual – port RAM)类型。 -

支持可选的输入和 / 或输出寄存器级。 -

支持的块存储器生成器(Block Memory Generator)内核特性包括: -

最小面积、固定原语和低功耗算法 -

复用器流水线级 -

嵌入式原语寄存器 -

内核输出寄存器 -

可选使能输入

-

-

实现了完全参数化,以优化资源利用。

-

-

BuiltIn ECC:内置纠错码,适用以下限制条件:-

字节写使能功能不可用。 -

所有端口宽度必须相同。 -

选择 “公共时钟” 选项时,支持 “读优先” 操作模式。 -

“使用 RST [A|B] 引脚” 和 “输出复位值” 选项不可用。 -

不支持存储器初始化。 -

无法进行算法选择。 -

不支持生成 32 位地址接口。

-

Error Injection Pins:错误注入引脚

-

Single Bit Error Injection:单 bit 错误注入 -

Double Bit Error Injection:双 bit 错误注入 -

Single and Double Bit Error Injection:单 bit 和双 bit 错误注入

说明:一般情况下,不需要使能 ECC 功能。

1.3 写使能(Write Enable)

Byte Write Enable:字节写使能。

Byte Size (bits):字节 bit 数,可选 8/9, 正常一个字节为 8bits,这里的 9bits 是 8bits + 1bit 奇偶校验。

是否需要使能字节写功能?或者说字节写有什么好处呢?下面进行说明。

字节写的优势

-

精细化的数据控制

-

按需修改:当存储器的数据位宽较大(如 32 位或 64 位)时,若只需修改其中部分字节(例如更新某个寄存器的低 8 位),字节写功能可以避免对无关字节的重复写入,减少数据总线的带宽占用。 -

减少功耗:仅更新目标字节而非整个字(Word),可降低动态功耗,适用于低功耗设计。 -

提升效率:若 BRAM 不支持字节写,修改部分字节需先读取整个数据字,修改目标字节后再写回。这会引入额外的延迟和潜在的并发访问冲突,直接通过写使能掩码(如WE[3:0])指定需更新的字节,无需中间读操作,提升效率,避免了读-修改-写(Read-Modify-Write)开销。

-

兼容处理器总线操作

-

支持标准总线协议:如 AXI、AHB 等总线协议允许按字节寻址(例如 AXI 的WSTRB信号)。通过字节写功能,BRAM 可直接对接这些总线,无需额外的数据掩码逻辑。 -

简化软件交互:在处理器(如 ARM、RISC-V)与 FPGA 协同设计中,软件可通过标准 C 语言指针操作(如uint8_t *ptr)直接修改特定字节,硬件无需软件侧的数据拼接或移位。

字节写的劣势

-

逻辑资源消耗更多:字节写功能需额外的多路选择器(MUX)和写使能控制逻辑,可能轻微增加 LUT 资源消耗。 -

外部写控制更繁琐:原本是单 bit 写使能控制写,现在是多 bit 写使能控制每个字节写,控制更复杂了。

说明:

-

当此 RAM 需要与外部软件语言(如 C 语言)或者一些支持字节写的总线进行交互时,可以使能字节写 -

进行低功耗设计时,可考虑使能字节写

1.4 架构选项(Algorithm Options)

Defines the algorithm used to concatenate the block RAM primitives. Refer datasheet for more information.

定义了用于拼接块随机存取存储器(Block RAM)原语的算法。更多信息请参考数据手册。

Algorithm(算法)

-

Minimum Area:最小面积,默认选择 -

Low Power:低功耗 -

Fixed Primitives:固定原语

Primitive(原语)

当算法选择固定原语时,原语可选:

-

2kx9 -

1kx18 -

512×36

说明:一般选择默认的最小面积即可,在意功耗则选择低功耗。

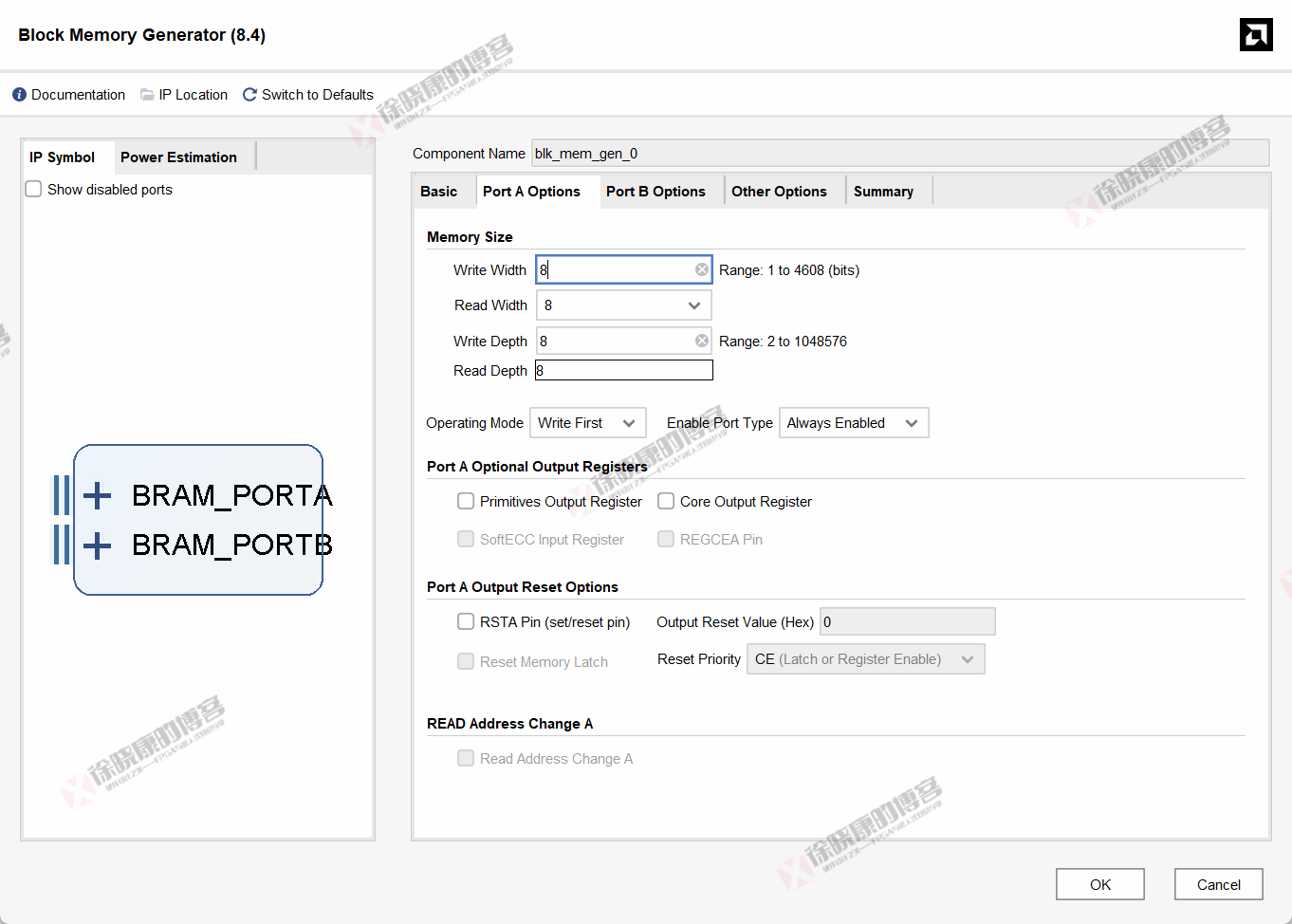

二、Port A Options(端口 A 选项)

2.1 存储大小(Memory Size)

Write Width:写位宽,一般取值范围为 1~4096,当使能字节写时,位宽必须为 8/9 的倍数。

Read Width:读位宽,此 RAM 集成了位宽转换功能,读位宽可以为写位宽的 1/32(最小)、1/16、1/8、1/2、1/1、2/1、4/1(最大)。

Write Depth:写深度,与芯片资源有关,最小为 2。

Read Depth:读深度,自动计算,等于写位宽 * 写深度 / 读位宽。

操作模式(Operating Mode):

-

Write First:写优先 -

Read First:读优先 -

No Change:无变化

使能端口类型(Enable Port Type):

-

Always Enabled,总是使能

-

Use ENA Pin:用使能引脚,端口信号出现 ENA 或 ENB,用于数据读取使能控制

操作模式建议

操作模式关键区别总结:

| 模式 | 写入时输出行为 | 资源占用 | 适用场景 |

|---|---|---|---|

| Write First | 输出当前写入的数据 | 低 | 高速写入、允许部分数据更新 |

| Read First | 输出地址中旧数据(写入后更新) | 较高 | 数据一致性要求高、多端口访问 |

| No Change | 输出保持不变 | 最低 | 保持输出稳定、避免抖动 |

操作模式选择建议:

-

如果 性能优先(如最小延迟、低资源占用),且可以容忍写入期间的输出变化,选择 Write First。 -

如果 可靠性优先(如多端口访问、数据一致性),选择 Read First。 -

如果 输出稳定性至关重要(如接口协议约束),选择 No Change。

使能端口建议

使能端口模式对比表:

| 属性 | Always Enabled | Use ENA Pin |

|---|---|---|

| 行为描述 | 读写端口始终有效,BRAM 始终响应地址和数据输入,无需外部控制信号。 | 读写操作由 ENA/ENB 信号控制,仅当使能信号为高电平时,BRAM 执行操作。 |

| 接口信号 | 无 ENA/ENB 引脚,接口简化。 |

需连接 ENA/ENB 引脚,由外部逻辑驱动使能信号。 |

| 核心特点 | – 无需额外控制逻辑 – 接口简单,资源占用少 – 功耗较高(始终激活) |

– 灵活控制访问时机 – 支持动态功耗管理 – 需外部信号同步 |

| 适用场景 | 1. 需要 持续访问 的存储(如寄存器文件) 2. 简单逻辑或无动态控制需求的设计 |

1. 需 分时复用存储(多模块共享) 2. 低功耗设计(动态关闭未使用访问) 3. 总线协议对接(如 AXI 的 Valid 信号) |

| 典型应用案例 | – 实时数据流处理(如无中断流水线) – 固定配置的查找表(LUT) |

– 多通道数据采集(分时使能) – 处理器缓存控制(按需访问) – 低功耗传感器节点 |

| 设计复杂度 | 低 | 中(需生成/管理使能信号) |

| 功耗影响 | 较高(BRAM 始终处于活跃状态) | 较低(可通过使能信号关闭非活动访问) |

关键设计建议:

-

Always Enabled: -

适用于 接口简单、实时性要求高 的设计,如持续读写的数据缓冲或固定配置存储。 -

注意:长期活跃可能增加系统功耗,需在功耗预算允许下使用。

-

-

Use ENA Pin: -

适用于 资源复用、动态控制或低功耗 场景,如多模块共享存储或间歇性数据访问。 -

需在时序约束中明确 ENA/ENB信号与时钟的关系,避免亚稳态。

-

2.2 端口 A 可选输出寄存器(Port A Optional Output Registers)

原语输出寄存器(Primitives Output Register)

原语输出寄存器:可分别选择在端口 A 和端口 B 的存储器原语之后插入输出寄存器。在独立模式下,“原语输出寄存器”选项被设置为默认选项。如果您选择对存储器原语的输出进行寄存,将使用块 RAM 原语中嵌入的输出寄存器。有关更多信息,请参阅附录 D 中的“输出寄存器配置”。

内核输出寄存器(Core Output Register)

为每个端口(A 或 B)进行选择,以便在该端口的存储器内核输出端插入一个寄存器。选中此选项时,将使用 FPGA 切片来实现寄存器,从而对内核输出进行寄存。

软件 ECC 输入寄存器(SoftECC Input Register)

使能流水线寄存器以提高最大频率。 仅适用于端口 B

REGCEA 引脚(REGCEA Pin)

选择使用单独的 REGCEA 或 REGCEB 输入引脚来控制存储器中最后一级输出寄存器的使能。未选中此选项时,所有寄存器级均由 ENA/ENB 使能。

2.3 端口 A 输出复位选项(Port A Output Reset Options)

复位 A 引脚(RSTA Pin (set/reset pin))

选择是否需要设置/复位引脚(RST [A|B])。

输出复位值(Output Reset Value (Hex))

指定存储器输出锁存器和输出寄存器的复位值。这些值是相对于读端口宽度而言的。

复位存储锁存(Reset Memory Latch)

修改复位操作的行为,并改变复位值的有效时长。根据此选项的选择,复位有效时长的最小值会作为信息显示在 Vivado 集成开发环境(IDE)中。有关“复位存储器锁存器”选项的更多信息,请参阅第 3 章中的“特殊复位行为”。

注意:仅当选择了相应端口的 “使用复位(RST)引脚” 选项和 “存储器原语输出寄存” 选项,且未选择相应端口的 “存储器内核寄存” 选项时,每个端口的 “复位行为(复位存储器锁存器)” 选项才可用。

复位优先级 CE(锁存或寄存器使能)(Reset Priority CE (Latch or Register Enable))

仅当选择了相应端口的“使用复位(RST)引脚”选项时,每个端口的“复位优先级”选项才可用。你可以将复位优先级设置为时钟使能(CE)或置位/复位(SR)。有关复位优先级功能的更多信息,请参阅第 3 章中的“复位优先级”。

2.4 读地址变化 A(READ Address Change A)

此功能仅适用于 UltraScale 系列器件。这是一项节能功能,可启用块随机存取存储器(block RAM)内部的读地址更改(比较)检测电路。当 RDADDRCHANGE(读地址更改信号)为真,且读地址和输出寄存器与上一个读周期相同时,将会产生相同的输出。因此,为节省功耗,不会执行对块 RAM 的访问操作。如果您一直保持块 RAM 处于启用状态,此功能将非常有用。仅当“公共时钟选项”设置为“真”时,此功能才可用。在任何时间点,RDADDRCHANGEA 和 RDADDRCHANGEB 都应设置为相同的值,也就是说,二者都应设置为“真”或“假”。

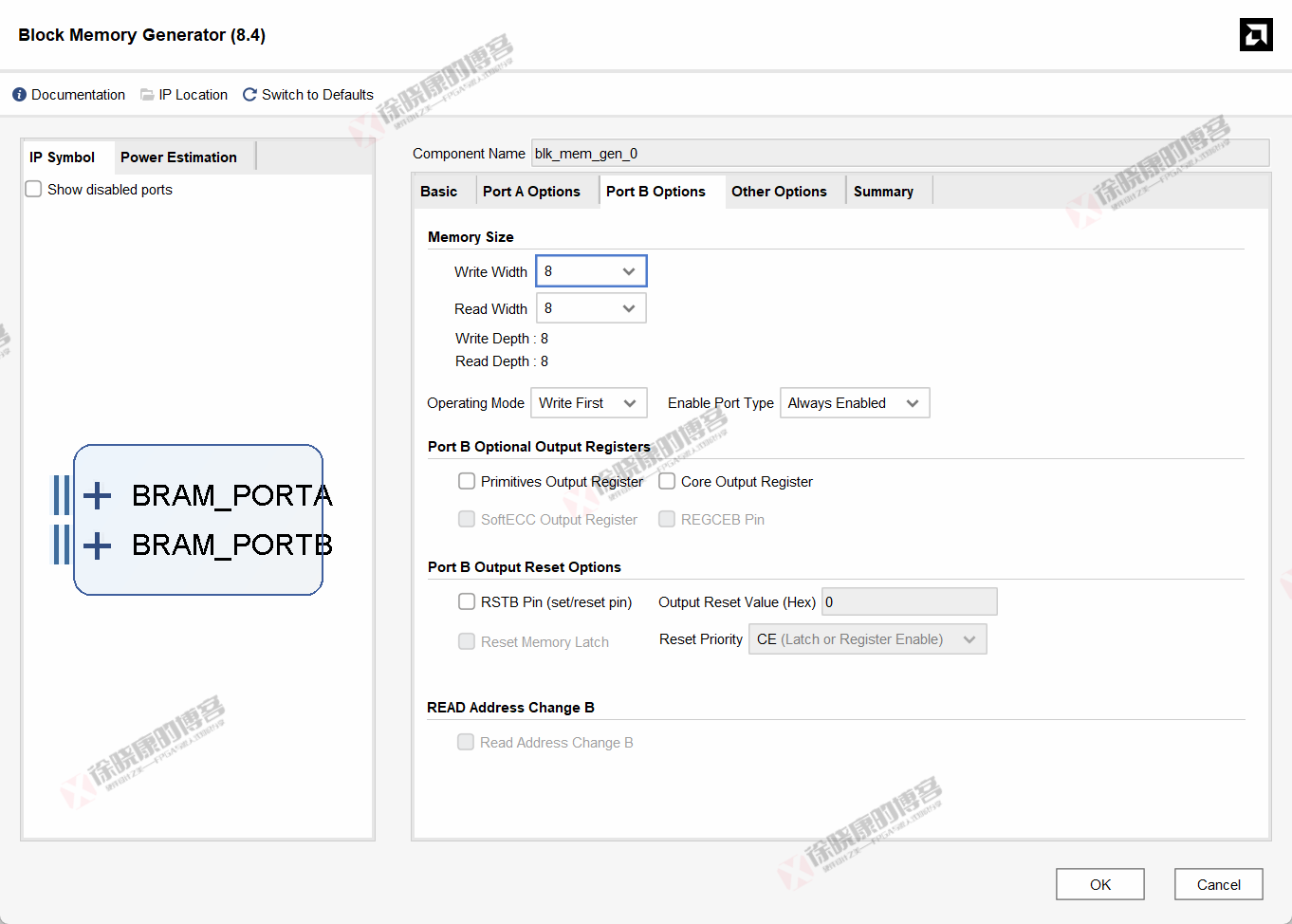

三、Port B Options(端口 B 选项)

配置方法与 Port A Options 相同。

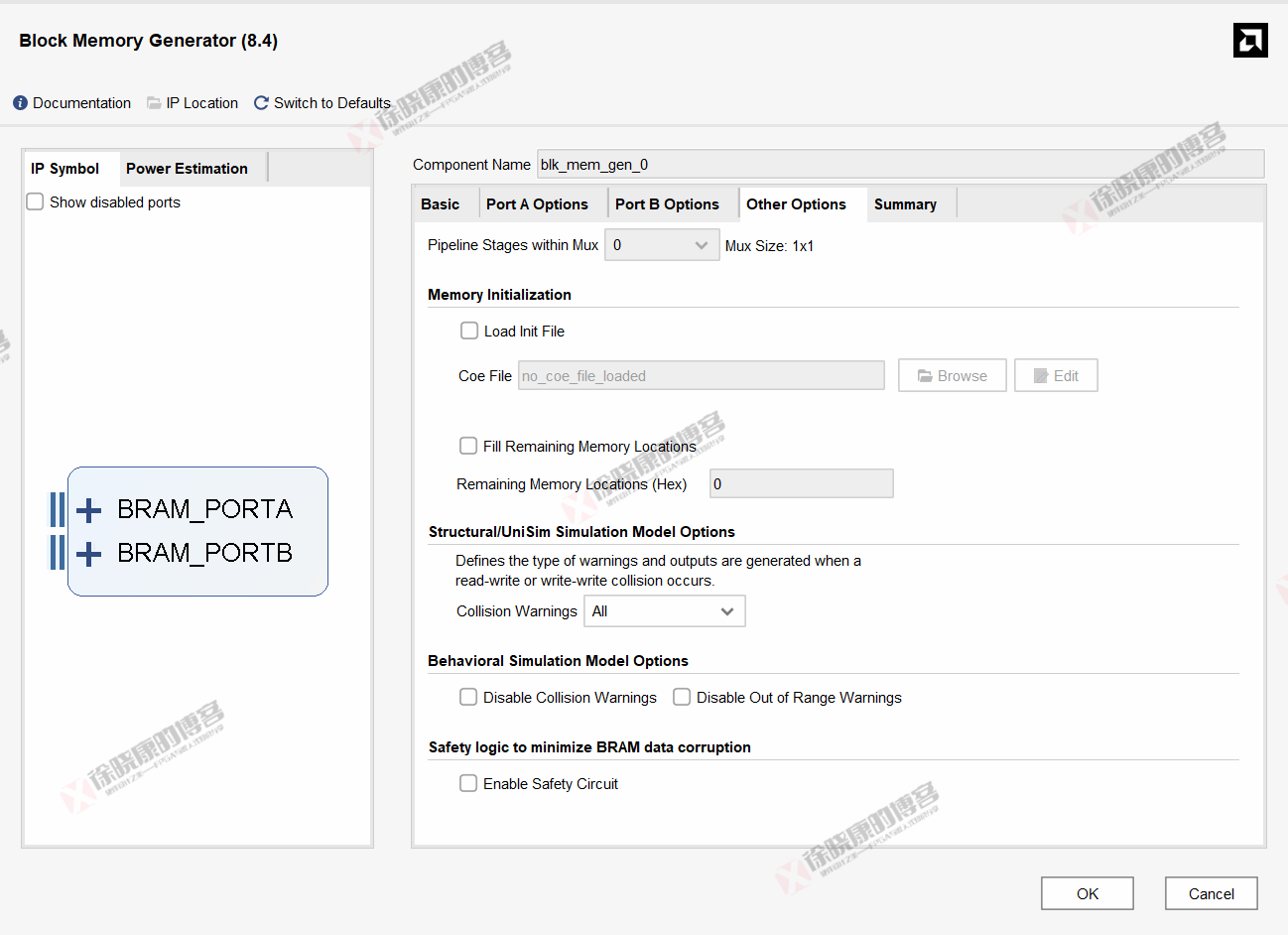

四、Other Options(其它选项)

Pipeline Stages within Mux()带有多路复用器的流水线级别)

仅当端口 A 和端口 B 都选择了“存储器内核输出寄存”选项,并且所构建的存储器在深度上包含多个原语,从而在输出端需要一个多路复用器(MUX)时,此选项才可用。从下拉列表中选择 0、1、2 或 3 中的一个值。

在 Vivado 集成开发环境(IDE)中显示的多路复用器大小可用于确定在该多路复用器内使用的流水线级数。根据器件架构,为您的设计选择合适的流水线级数。

存储器初始化(Memory Initialization)

-

load Init File:载入初始化文件 -

Coe File:Coe 文件 -

Fill Remaining Memory Locations:填充剩余存储位置

选择是否使用 COE 文件来初始化存储器内容,以及是否使用默认值来初始化其余的存储器内容。当使用非对称的端口宽度或数据宽度时,COE 文件和默认值是相对于端口 A 的写入宽度而言的。更多详细信息,请参阅“指定初始存储器内容”。

结构型/统一仿真器仿真模型选项(Structural/UniSim Simulation Model Options)

定义当发生读-写冲突 或 写-写冲突时所生成的警告类型和输出内容。

冲突警告(Colision Warnings):

-

All -

None -

Warning Only -

Generate X-Only

选择在发生冲突时,由结构仿真模型生成的警告消息类型和输出内容。对于“全部(ALL)”、“仅警告(WARNING_ONLY)”和“仅生成不确定值(GENERATE_X_ONLY)”这些选项,UNISIM 模型中的冲突检测功能会被启用,以便在任何条件下处理冲突情况。

“无(NONE)”选项适用于那些不存在冲突,并且时钟(端口 A 和端口 B)永远不会同相,或者时钟偏移在 3000 皮秒(ps)以内的设计。如果选择了“无(NONE)”,模型中的冲突检测功能将被禁用,冲突期间的行为将由模拟器来处理。因此,如果时钟同相、来自同一时钟源,或者时钟偏移在 3000 皮秒以内,并且两个端口的地址相同,那么输出将是不可预测的。“无(NONE)”选项是为时钟永远不同相的设计准备的。

行为仿真模型选项(Behavioral Simulation Model Options)

Disable Collision Warnings:选择由行为仿真模型生成的警告消息的类型。

Disable Out of Range Warnings:选择该模型在发出冲突警告时是否应假定为同步时钟(公共时钟)。

安全电路(Safety Circuit)

安全电路:块存储器生成器知识产权核(Block Memory Generator IP)包含一个内置的安全电路。当块随机存取存储器(BRAM)的输入信号(如端口使能信号(ena|b)、端口地址信号(addra|b)、数据输入信号(dina|b)、写使能信号(wea|b)、复位信号(rsta|b)等)出现建立/保持时间违规情况时,该安全电路可将 BRAM 数据损坏的发生概率降至最低。当选择了复位选项时,块存储器生成器总会选择安全电路选项,并建议用户使所有输入信号与端口时钟(CLKA|B)同步驱动。块存储器生成器的安全电路包含两个输出端口rsta_busy和rstb_busy,用于在这些信号有效时指示不应访问BRAM。只有当从知识产权核接口中选择了安全电路选项时,这些端口才可用。有关 BRAM 数据损坏的更多详细信息,请参阅解答记录:42571。

注意:当使用内核输出寄存器时,不支持安全电路功能。

指定初始存储器内容

块存储器生成器内核支持在 Vivado 集成开发环境(IDE)中使用存储器系数(COE)文件、默认数据选项或两者结合的方式对存储器进行初始化。COE 文件可以指定每个存储单元的初始内容,而默认数据则指定所有存储单元的内容。当两者配合使用时,COE 文件可以指定部分存储空间的内容,而默认数据则填充其余的存储空间。COE 文件和默认数据的格式是相对于端口 A 的写入宽度(对于只读存储器(ROM)则是端口 A 的读取宽度)而言的。

COE 文件是一种文本文件,它指定了两个参数:

-

memory_initialization_radix: memory_initialization_vector中值的基数。有效选项为 2、10 或 16。 -

memory_initialization_vector:定义每个存储单元的内容。每个值按最低有效位(LSB)对齐,并且假定采用 memory_initialization_radix所定义的基数。

以下是一个 COE 文件的示例。请注意,分号是行结束符。

8 位宽、深度为 16 的随机存取存储器(RAM)的示例初始化文件:

memory_initialization_radix = 16;

memory_initialization_vector =

12, 34, 56, 78, AB, CD, EF, 12, 34, 56, 78, 90, AA, A5, 5A, BA;

系数之间可以用空格、逗号分隔,也可以每行放置一个值并使用回车分隔。

要使用块存储器生成器(BMG)接口创建 COE 文件,请转到如图 4 – 3 所示的“其他选项”选项卡中的存储器初始化部分。

-

选择/勾选“加载初始化文件”。 -

点击“编辑”。 -

创建或选择一个文件。 -

输入所需的 memory_initialization_radix和memory_initialization_vector。

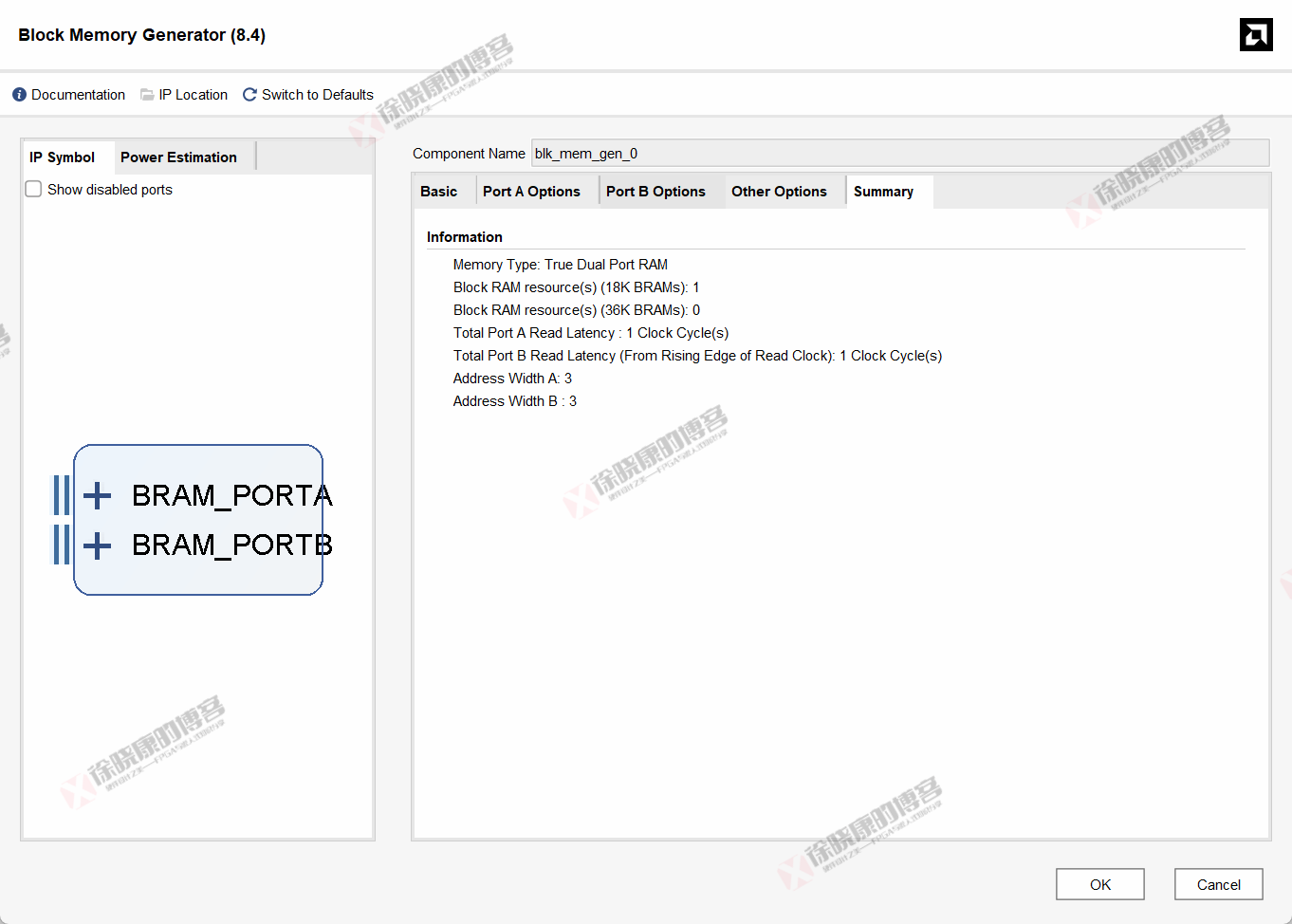

五、Summary(总结)

块随机存取存储器(Block RAM)的使用情况

“摘要”选项卡会报告实际要使用的 18K 和 36K 块随机存取存储器块的数量。当使用固定原语算法时,为了估算该数值,所使用的块随机存取存储器原语的数量等于宽度比率(向上取整)乘以深度比率(向上取整)。其中,宽度比率是存储器的宽度除以所选原语的宽度,深度比率是存储器的深度除以所选原语的深度。

当使用低功耗算法时,估算块随机存取存储器的使用情况需要进行更多计算:

-

如果存储器宽度是所选架构中可用的最宽原语宽度的整数倍,那么使用的原语数量的计算方法与固定原语算法相同。宽度比率和深度比率是使用最宽原语的宽度和深度来计算的。例如,对于一个配置为 2kx72 的存储器,使用最宽为 512×36 的原语时,宽度比率为 2,深度比率为 4。因此,使用的可用原语总数为 8 个。 -

如果存储器宽度大于最宽原语宽度的整数倍,那么除了上述计算得出的原语数量之外,还需要更多原语来覆盖剩余的宽度。这个额外的数量是通过将存储器深度除以为覆盖剩余宽度而选择的额外原语的深度来得到的。例如,一个配置为 17kx37 的存储器,需要一个 512×36 的原语来覆盖 36 的宽度,还需要一个额外的 16kx1 的原语来覆盖剩余的 1 的宽度。为了覆盖 17K 的深度,需要 34 个 512×36 的原语和 2 个 16kx1 的原语。因此,对于这种配置,使用的原语总数为 36 个。 -

如果存储器宽度小于最宽原语的宽度,那么就会选择能够覆盖存储器宽度的最小可能原语来解决问题。使用的原语总数是通过将存储器深度除以所选原语的深度来得到的。例如,对于一个配置为 2kx32 的存储器,选择的原语是 512×36,使用的原语总数是 2k 除以 512,即 4 个。

当使用最小面积算法时,要确定确切的块随机存取存储器数量就没那么容易了。这是因为实际算法会进行复杂的操作以得出最优解决方案。对 18K 块随机存取存储器数量的乐观估算方法是,将存储器的总位数除以 18K(每个原语的总位数),然后向上取整。鉴于这种算法能够非常高效地组合块随机存取存储器,对于大多数存储器来说,这种估算通常是非常准确的。

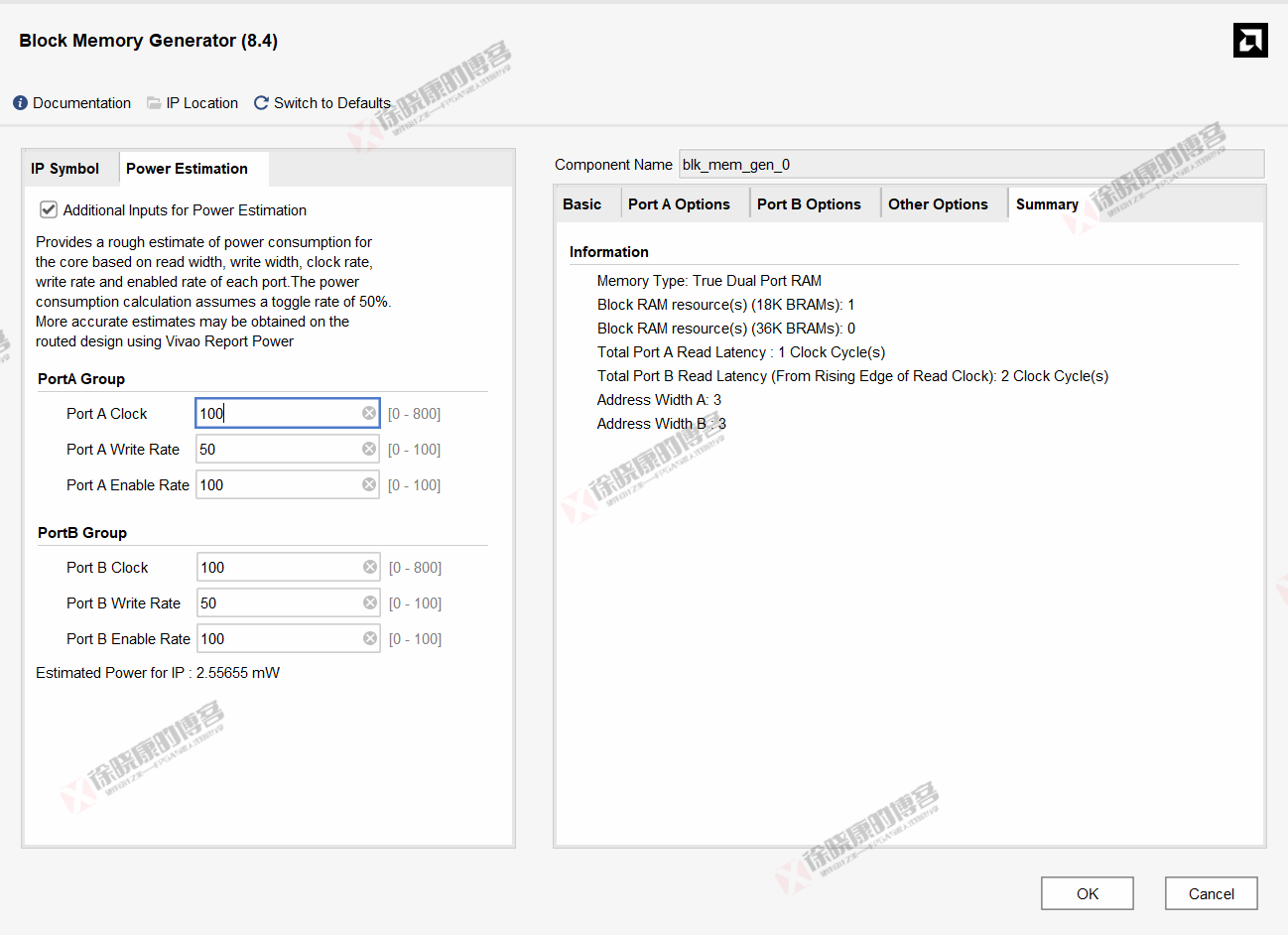

六、功耗估算(Power Estimation)

如图 4-6 所示,Vivado 集成开发环境(IDE)左侧的“功耗估算”选项卡,会根据每个端口已配置的读取宽度、写入宽度、时钟频率、写入速率和使能速率,对内核的功耗进行大致估算。功耗计算假定翻转率为 50%。使用 XPower 分析器工具,对完成布线的设计可以获得更精确的估算结果。有关 XPower 分析器的更多信息,请访问 www.xilinx.com/power。

除了配置参数之外,此选项卡还有一个“功耗估算附加输入”选项。你可以输入以下参数用于功耗计算:

-

**时钟频率 [A|B]**:分别为端口 A 和端口 B 的工作时钟频率。 -

**写入速率 [A|B]**:分别为端口 A 和端口 B 的写入速率。 -

**使能速率 [A|B]**:分别为端口 A 和端口 B 的平均访问速率。

总结与参考

本文大部分为 PG058-Chapter 4-Design Flow Steps 的中文翻译,部分内容添加了一些基于个人理解的说明,希望对各位同学理解和使用 BRAM IP 有些帮助。

但必须要说明的是,最好的理解方式是实际综合此 IP,然后上板测试,再 通过ILA观察IP行为,将行为与手册的说明进行验证,这样才能对此 IP 有更好的理解。

上板实测 IP 的内容,可参考我的其它博客:

Verilog 功能模块–RAM 和 ROM(02)–同步写-写冲突与读-写冲突实测

Verilog 功能模块–RAM 和 ROM(03)–自编 RAM 与 Vivado RAM IP 功能对比实测

相关参考:

-

pg058-blk-mem-gen.pdf

-

ug473_7Series_Memory_Resources.pdf

-

ug901-vivado-synthesis-en-us-2024.2.pdf

AMD 官网可下载最新版。

如果本文对你有所帮助,欢迎点赞、转发、收藏、评论让更多人看到,赞赏支持就更好了。

如果对文章内容有疑问,请务必清楚描述问题,留言评论或私信告知我,我看到会回复。

徐晓康的博客持续分享高质量硬件、FPGA与嵌入式知识,软件,工具等内容,欢迎大家关注。